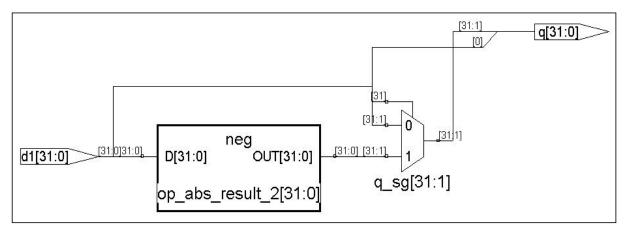

Figure 6.1.1-14 RTL View of Absolute Model (Synplicity/Synplify Pro)

The question often arises as to the whether the NUMERIC\_STD or NUMERIC\_UNSIGNED package should be used when operating on UNSIGNED objects defined as STD\_LOGIC\_VECTOR types. Die-hard users who like to emphasize the language strong typing characteristics prefer to restrict the modeling with the NUMERIC\_STD only. An explicit type conversion is needed as shown in the previous models. However, users with either a Verilog background, or who prefer to maintain code compactness without violating the strong typing rules would prefer to use the NUMERIC\_UNSIGNED package.

## 6.2 VERILOG ARITHMETIC

Verilog 1364-1995 arithmetic operations were upgraded in the 1364-2001 Language Reference Manual. As of the date of this publication, all HDL synthesis companies support the Verilog 1364-1995 with the synthesis restrictions. However, a few companies are beginning to support many of the features of the 2001 LRM, and it is anticipated that all synthesis companies will fully embrace the new standard. In addition, the *Verilog Synthesis Interoperability Working Group of the Design Automation Standards Committee*<sup>50</sup> is currently refining the IEEE P1364 Standard for Verilog Register Transfer Level Synthesis. This standard describes a standard syntax and semantics for Verilog HDL based RTL synthesis. It defines the subset of IEEE 1364-2001 (Verilog HDL) that is suitable for RTL synthesis and defines the semantics of that subset for the synthesis domain.

This section is divided into two subsections. Subsection 6.2.1 addresses the arithmetic operations with the 1995 LRM, whereas subsection 6.2.2 provides some of the new arithmetic features of Verilog 2001. This section is not intended to describe Verilog 2001, as this is fully documented in the *IEEE Standard Hardware Description Language Based on the Verilog Hardware Description Language*.

## 6.2.1 Verilog 1364-1995 Arithmetic

<sup>&</sup>lt;sup>50</sup> http://www.eda.org/vlog-synth/ IEEE PAR 1364.1

## 6.2.1.1 Understanding Types and Numbers

Verilog defines two data types: **nets**(or *wire*) and *reg*. A *net* represents a physical connection between structural entities and is of a resolved data type, meaning that the final value will be the resolution of all the sources (i.e., drivers) asserting a value onto the net. <u>A *net* object is treated as an UNSIGNED</u> number object and loses the significance of the SIGN bit.

A *reg* is an "abstraction of a data storage element" and may store a value. For synthesis, a *reg* type includes the *reg* and *integer* declarations. An object asserted a value in an *always* or *initial* block must be of type *reg* (synthesis ignores the *initial statement*). In addition, a local object of a *task* or *function* must also be of type *reg*. A *reg* object is unresolved and can be assigned a value from different *always* or *initial* blocks. However, for synthesis, a *reg* type can only be assigned in only one *always* block (excluding *task* and *function*). A *reg* object can be a discrete one bit, or a vector (e.g., an array of bits), or a memory (i.e., one-dimensional array of vectors).

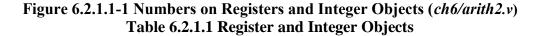

An object of type *reg* is processed by Verilog as an UNSIGNED number, however, it can be assigned a negative constant. Negative numbers are represented in 2's complement form. A reg object loses the significance of the SIGN bit. An object of type *integer* is processed by Verilog as a SIGNED number and retains the significance of the sign. The difference between SIGNED and UNSIGNED number is in SIGN or ZERO extension of the left most bits when arithmetic and logical operations are performed. Section 4.4.1 of the Verilog LRM specifies the rules for expression bit lengths. For "+ - / % &  $|^{\ }\sim -^{\ }$ " arithmetic operations, and for "=== !== !=  $\&\& \parallel >> = < =$ " logical operations, the number of bits used in the expression evaluations is the maximum of the length of the left operand and the right operand. Remember that an *integer* value is a 32-bit value, whereas a sized value is defined by the value of the size. Decimal numbers are signed. Based-numbers (e.g., 4'h21) are unsigned. An UNSIZED value (e.g., 'h5) is 32 bits. Unsized unsigned constants, where the high order bit is unknown (e.g., X or x) or tri-state (Z or z), are extended to the size of the expression containing the constant. If the size of the unsigned number is smaller than the size specified for the constant (e.g. intA32bits = hF;), the unsigned number is padded to the left with zeros (e.g., intA32bits = 32'h0000 000F;). If the leftmost bit in the unsigned number is an x or a z, then an x or a z is used to pad to the left respectively. These concepts are demonstrated in Figure 6.2.1.1-1 and 6.2.1.1-2. Table 6.2.1.1 provides an explanation of the results for the simulation of Figure 6.2.1.1-1.

```

module arith2;

integer intA;

reg [15:0] regA;

always @ (intA or regA)

$display($time, '' intA = %h, regA= %h'', intA, regA);

initial

```

```

begin

#50 intA = -4'd12;

#50 regA = intA / 3; // expression result is -4,

// intA is an integer data type, regA is 65532

#50 regA = -4'd12; // regA is 65524

#50 intA = regA / 3; // expression result is 21841,

// regA is a reg data type

#50 intA = -4'd12 / 3;// expression result is 1431655761.

// -4'd12 is effectively a 32-bit reg data type

#50 regA = -12 / 3; // expression result is -4, -12 is effectively

// an integer data type. regA is 65532

#50 regA = 'h1z;

#50 intA = 'h1z;

#50 regA = 'hz;

#50 intA = 'hz;

#50 regA ='hf;

#50 intA = 'hf;

#500 regA = 'h0;

end

endmodule //

/* -----\/----- EXCLUDED -----\/-----

NC-Sim> run 1 us

50 intA = fffffff4, regA= xxxx

100 intA = fffffff4, regA= fffc

150 intA = fffffff4, regA= fff4

200 intA = 00005551, regA= fff4

250 intA = 55555551, regA= fff4

300 intA = 55555551, regA= fffc

350 intA = 55555551, regA= 001z

400 intA = 0000001z, regA= 001z

450 intA = 0000001z, regA= zzzz

500 intA = zzzzzzzz, regA= zzzz

550 intA = zzzzzzz, regA= 000f

600 intA = 0000000f, regA= 000f

----/\----- EXCLUDED -----/\----- */

```

| integer intA;<br>reg [15:0] regA;IntA is 32 bits<br>regA is 16 bitsObject decalrationintA = -4'd12;intA = FFFF_FFF4 $4'd12 = 0000\_000C //$ unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a<br>// a 32-bit vector<br>= 2's complement of the 32-bit vector<br>= 2's complement(0000\_000C) = FFFF_FFF4regA = intA / 3;regA= FFFCintA is a SIGNED integer number<br>intA / 3 = FFFF_FFC<br>// regA is a 16-bit UNSIGNED register<br>regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF44'd12 = 000C_// unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>= 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000\_5551// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000\_5551intA = -4'd12 / 3;intA = 5555\_55514'd12 = 000C_// unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>= 2's complement of the 32-bit vector<br>= 2's complement(000C) = FFFF_FFF4intA = -4'd12 / 3;intA = 5555\_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>= 2's complement of the 32-bit vector<br>= 2's complement(000C) = FFFF_FFF4regA = -12 / 3regA = FFFC// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OPERATION          | VALUE                                 | COMMENTS                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|-------------------------------------------------|

| reg [15:0] regA;regA is 16 bitsintA = -4'd12;intA = FFFF_FFF44'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a<br>// a 32-bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_000C) = FFFF_FFF4regA = intA / 3;regA= FFFCintA is a SIGNED integer number<br>intA / 3 = FFFF_FFFC<br>// regA is a 16-bit UNSIGNED register<br>regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>-4'd12 = 2's complement of the 16-bit vector<br>-4'd12 = 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>= 2's complement of the 32-bit vector<br>= 2's complement (0000_000C) // assigned onto a // a 32-<br>bit vector<br>= 2's complement of the 32-bit vector<br>= 2's complement (0000_00C) = FFFF_FFF4<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement (0000_00C) = FFFF_FFF4<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement (0000_00C) = FFFF_FFF4intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_2'/ assigned onto a // a 32-<br>bit vector<br>-2's complement of the 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | integer intA;      | IntA is 32 bits                       | Object decalration                              |

| extended// to 32 bits because it will be assigned onto a// a 32-bit vector-4'd12 = 2's complement of the 32-bit vector= 2's complement (0000_000C) = FFFF_FF4regA = intA / 3;regA = -4'd12;regA = -12 / 3;intA = 5555_5551regA = -12 / 3;regA = -12 / 4;regA = -12 / 4; <td></td> <td>regA is 16 bits</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    | regA is 16 bits                       |                                                 |

| extended// to 32 bits because it will be assigned onto a// a 32-bit vector-4'd12 = 2's complement of the 32-bit vector= 2's complement (0000_000C) = FFFF_FF4regA = intA / 3;regA = -4'd12;regA = -12 / 3;intA = 5555_5551regA = -12 / 3;regA = -12 / 4;regA = -12 / 4; <td></td> <td>-</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | -                                     |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | intA = -4'd12;     | intA = FFFF_FFF4                      | $4'd12 = 0000\_000C$ // unsigned number in hex, |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                       | extended                                        |

| $\begin{array}{ c c c c c c } -4'd12 = 2's \ complement of the 32-bit vector \\ = 2's \ complement(0000_000C) = FFFF_FF4 \\ \hline regA = intA / 3; \\ regA = FFFC \\ \hline regA = -4'd12; \\ regA = -4'd12; \\ regA = -4'd12; \\ regA = FFF4 \\ \hline 4'd12 = 000C // \ unsigned number \ in hex, extended // \ to 16 \ bits \ because \ it \ will \ be \ assigned \ onto \ a \\ // a \ 16-bit \ vector \\ -4'd12 = 2's \ complement \ of \ the \ 16-bit \ vector \\ -4'd12 = 2's \ complement \ of \ the \ 16-bit \ vector \\ -4'd12 = 2's \ complement \ of \ the \ 16-bit \ vector \\ -4'd12 = 2's \ complement \ of \ the \ 16-bit \ vector \\ -2's \ complement \ of \ the \ 16-bit \ vector \\ -2's \ complement \ of \ the \ 16-bit \ vector \\ regA \ a \ FFF4 / 3 = 5551 \\ // \ regA \ is \ zero \ extended \ to \ 32 \ bit \ because \ it \ will \ be \\ // \ assigned \ onto \ a \ 32-bit \ regA \ a \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -4'd12 \ a \ 2's \ complement \ of \ the \ 32-bit \ vector \\ -2's \ complement \ 0's \ a \ a \ a \ a \ a \ a \ a \ a \ a \ $                                                                                                                                                                                                                                                              |                    |                                       |                                                 |

| $= 2's complement(0000_000C) = FFFF_FFF4$ $regA = intA / 3;$ $regA = FFFC$ $intA is a SIGNED integer number intA / 3 = FFFF_FFC // regA is a 16-bit UNSIGNED register regA = intA[15:0] = FFFC regA = -4'd12; regA = FFF4 4'd12 = 000C // unsigned number in hex, extended // to 16 bits because it will be assigned onto a // a 16-bit vector = 2's complement of the 16-bit vector = 2's complement(000C) = FFF4 intA = regA / 3; intA = 0000_5551 // regA is UNSIGNED FFF4 or 65524, positive number regA / 3 = FFF4 / 3 = 5551 // regA is zero extended to 32 bits because it will be // assigned onto a 32-bit register. Thus, intA = 0000_5551 intA = -4'd12 / 3; intA = 5555_5551 4'd12 = 0000_000C // unsigned number in hex, extended // to 32 bits because it will be assigned onto a // a 32-bit vector = 2's complement of the 32-bit vector = 2's complement(0000_000C) = FFFF_FFF4 -4'd12/3 = FFFF_FF4/3 = 5555_5551 regA = -12 / 3 regA = FFFC // regA = 001z // regA is 16 bits. 'h1z = 0001_zzzz, zero extended$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                       |                                                 |

| regA = intA / 3;regA= FFFCintA is a SIGNED integer number<br>intA / 3 = FFF_FFFC<br>// regA is a 16-bit UNSIGNED register<br>regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>-4'd12 = 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA / 3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_00C) = FFFF_FFF4<br>-4'd12/3 = FFFF_FF4/3 = 5555_5551regA = -12 / 3regA= FFFC<br>// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4<br>-12 = FFFF_FFF4<br>-12 = FFFF_FFF4regA = 'h1z;regA= 001z// regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                       | 1                                               |

| intA / 3 = FFF_FFC<br>// regA is a 16-bit UNSIGNED register<br>regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF4regA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>-4'd12 = 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000_5551intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_5551intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_000C) = FFFF_FFF4<br>= 4'd12/3 = FFFF_FF4/3 = 555_5551regA = -12 / 3regA= FFFCregA = 'h1z;regA= 001z// regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                       |                                                 |

| // regA is a 16-bit UNSIGNED register<br>regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>-4'd12 = 2's complement of the 16-bit vector<br>= 2's complement(000C) = FF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 /3 = 5551// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_5551intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_000C) = FFFF_FFF4<br>-4'd12/3 = FFFF_FF4/3 = 5555_551regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFFCregA = 'h1z;regA= 001z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | regA = intA / 3;   | regA= FFFC                            | C C                                             |

| regA = intA[15:0] = FFFCregA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>= 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_5551intA = -12 / 3regA = FFFC// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFFCintA = 'h1z;regA = 001z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                                       | _                                               |

| regA = -4'd12;regA= FFF44'd12 = 000C // unsigned number in hex, extended<br>// to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>= 2's complement of the 16-bit vector<br>= 2's complement(000C) = FFF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_000C) = FFFF_FFF4<br>-4'd12/3 = FFFF_FF4/3 = 5555_5551regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFFF4regA = 'h1z;regA= 001z// regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                       |                                                 |

| // to 16 bits because it will be assigned onto a<br>// a 16-bit vector<br>$-4'd12 = 2's$ complement of the 16-bit vector<br>$= 2's$ complement(000C) = FFF4intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>$-4'd12 = 2's$ complement of the 32-bit vector<br>$= 2's$ complement of the 32-bit vector<br>$= 2's$ complement (0000_000C) = FFFF_FFF4<br>$-4'd12/3 = FFFF_FFF4/3 = 5555_5551$ regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>$-12 = FFFF_FFF4$ (in hex)<br>$-12/3 = FFFF_FFF4$ (in hex)<br>$-12/3 = FFFF_FFF4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                       |                                                 |

| $ \begin{array}{ c c c c c c c c } // a 16-bit vector \\ -4'd12 = 2's complement of the 16-bit vector \\ = 2's complement(000C) = FFF4 \\ \hline intA = regA / 3; \\ intA = 0000\_5551 \\ // regA is UNSIGNED FFF4 or 65524, positive number \\ regA / 3 = FFF4 / 3 = 5551 \\ // regA is zero extended to 32 bits because it will be \\ // assigned onto a 32-bit register. Thus, \\ intA = 0000\_5551 \\ \hline intA = -4'd12 / 3; \\ intA = 5555\_5551 \\ 4'd12 = 0000\_000C // unsigned number in hex, \\ extended \\ // to 32 bits because it will be assigned onto a // a 32-bit vector \\ = 2's complement of the 32-bit vector \\ = 2's complement(0000\_000C) = FFFF\_FFF4 \\ -4'd12/3 = FFFF\_FFF4/3 = 5555\_5551 \\ \hline regA = -12 / 3 \\ regA = FFFC \\ \hline regA = 001z \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzz, zero extended \\ \hline // regA is 16 bits. h1z = 0001\_zzzzz, zero extended \\ \hline // regA is 16 bits = 0001\_zzzzz, zero extended \\ \hline // regA is 16 bits = 0001\_zzzz is 0001\_zzzzz, zero extended \\ \hline // regA is 16 bits = 0001\_zzzzz is 0001\_$ | regA = -4'd12;     | regA= FFF4                            | -                                               |

| $\begin{array}{ c c c c c c c c } & -4'd12 = 2's \ complement \ of \ the \ 16-bit \ vector \\ & = 2's \ complement(000C) = FFF4 \\ \hline intA = regA / 3; & intA = 0000\_5551 & // \ regA \ is \ UNSIGNED \ FFF4 \ or \ 65524, \ positive \ number \ regA / 3 = FFF4 / 3 = 5551 \\ & // \ regA \ is \ zero \ extended \ to \ 32 \ bits \ because \ it \ will \ be \\ & // \ assigned \ onto \ a \ 32-bit \ register. \ Thus, \\ & intA = 0000\_5551 \\ \hline intA = -4'd12 / 3; & intA = 5555\_5551 & 4'd12 = 0000\_000C \ // \ unsigned \ number \ in \ hex, \\ extended \\ & // \ to \ 32 \ bits \ because \ it \ will \ be \ assigned \ onto \ a \ \ // \ a \ 32-bit \ vector \\ & -4'd12 = 2's \ complement \ of \ the \ 32-bit \ vector \\ & -4'd12 = 2's \ complement \ of \ the \ 32-bit \ vector \\ & -4'd12/3 = FFFF\_FFF4/3 = 5555\_5551 \\ \hline regA = -12 / 3 & regA = FFFC & // \ -12 \ is \ an \ integer \ 32-bit \ number \\ & -12/3 = FFFF\_FFF4 \ (in \ hex) \\ & -12/3 = FFFF\_FFFC \\ \hline regA = 'h1z; & regA = 001z & // \ regA \ is \ 16 \ bits. \ 'h1z = 0001\_zzzz, \ zero \ extended \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                       | •                                               |

| $= 2's complement(000C) = FFF4$ intA = regA / 3; intA = 0000_5551 // regA is UNSIGNED FFF4 or 65524, positive number regA /3 = FFF4 / 3 = 5551 // regA is zero extended to 32 bits because it will be // assigned onto a 32-bit register. Thus, intA = 0000_5551 intA = -4'd12 / 3; intA = 5555_5551 4'd12 = 0000_000C // unsigned number in hex, extended // to 32 bits because it will be assigned onto a // a 32-bit vector -4'd12 = 2's complement(0000_000C) = FFFF_FF4 -4'd12/3 = FFFF_FF4/3 = 5555_5551 regA = -12 / 3 regA = FFFC regA = 'h1z; regA = 001z // regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |                                       |                                                 |

| intA = regA / 3;intA = 0000_5551// regA is UNSIGNED FFF4 or 65524, positive number<br>regA /3 = FFF4 / 3 = 5551<br>// regA is zero extended to 32 bits because it will be<br>// assigned onto a 32-bit register. Thus,<br>intA = 0000_5551intA = -4'd12 / 3;intA = 5555_55514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>-4'd12 = 2's complement of the 32-bit vector<br>= 2's complement(0000_000C) = FFFF_FFF4<br>-4'd12/3 = FFFF_FF4/3 = 5555_5551regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>-12 = FFFF_FFF4 (in hex)<br>-12/3 = FFFF_FFFCregA = 'h1z;regA= 001z// regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                                       | *                                               |

| $regA /3 = FFF4 / 3 = 5551$ $// regA is zero extended to 32 bits because it will be // assigned onto a 32-bit register. Thus, intA = 0000_5551$ intA = -4'd12 / 3; intA = 5555_5551 $d'd12 = 0000_000C // unsigned number in hex, extended // to 32 bits because it will be assigned onto a // a 32-bit vector -4'd12 = 2's complement of the 32-bit vector = 2's complement(0000_000C) = FFFF_FFF4 -4'd12/3 = FFFF_FFF4/3 = 5555_5551$ $regA = -12 / 3$ $regA = FFFC$ $// -12 is an integer 32-bit number -12 = FFFF_FF4 (in hex) -12/3 = FFFF_FFF4 (in hex) -12/3 = FFFF_FFFC$ $regA = 'h1z;$ $regA = 001z$ $// regA is 16 bits. 'h1z = 0001_zzzzz, zero extended$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                       |                                                 |

| $ \begin{array}{ c c c c c c c c } \label{eq:constraint} & \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | intA = regA / 3;   | $intA = 0000_{5551}$                  |                                                 |

| $ \begin{array}{ c c c c c c c } & & & & & & & & & & & & & & & & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                       |                                                 |

| $intA = 0000_{5551}$ $intA = -4'd12 / 3;$ $intA = 5555_{5551}$ $4'd12 = 0000_{000C} // \text{ unsigned number in hex,}$ $extended$ $// \text{ to 32 bits because it will be assigned onto a // a 32-bit vector$ $-4'd12 = 2'\text{s complement of the 32-bit vector}$ $= 2'\text{s complement}(0000_{000C}) = \text{FFFF}_{FF4}$ $-4'd12/3 = \text{FFFF}_{FF4}/3 = 5555_{5551}$ $regA = -12 / 3$ $regA = \text{FFFC}$ $// -12 \text{ is an integer 32-bit number}$ $-12 = \text{FFFF}_{FF4} (\text{ in hex})$ $-12/3 = \text{FFFF}_{FF7}$ $regA = 001z$ $// regA \text{ is 16 bits. 'h1z} = 0001_{zzzzz, zero extended}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                       | -                                               |

| intA = -4'd12 / 3;intA = 5555_5514'd12 = 0000_000C // unsigned number in hex,<br>extended<br>// to 32 bits because it will be assigned onto a // a 32-<br>bit vector<br>$-4'd12 = 2$ 's complement of the 32-bit vector<br>$= 2$ 's complement(0000_000C) = FFFF_FF4<br>$-4'd12/3 = FFFF_FF4/3 = 5555_5551$ regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>$-12 = FFFF_FF4$ (in hex)<br>$-12/3 = FFFF_FF4$ (in hex)<br>$-12/3 = FFFF_FF4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                       |                                                 |

| extended// to 32 bits because it will be assigned onto abit vector-4'd12 = 2's complement of the 32-bit vector= 2's complement (0000_000C) = FFFF_FF4-4'd12/3 = FFFF_FF4/3 = 5555_5551regA = -12 / 3regA = FFFC// -12 is an integer 32-bit number-12 = FFFF_FF4 (in hex)-12/3 = FFFF_FF4 (in hex)-12/3 = FFFF_FFFCregA = 'h1z;regA = 001z//regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ···· 41110 / 2.    |                                       |                                                 |

| $ \begin{array}{ c c c c c c } & // \ to \ 32 \ bits \ because \ it \ will \ be \ assigned \ onto \ a \ // \ a \ 32-bit \ vector \\ & -4'd12 = 2's \ complement \ of \ the \ 32-bit \ vector \\ & = 2's \ complement \ (0000\_000C) = FFFF\_FFF4 \\ & -4'd12/3 = FFFF\_FFF4/3 = 5555\_5551 \\ \hline regA = -12 \ / \ 3 & regA = FFFC & // \ -12 \ is \ an \ integer \ 32-bit \ number \\ & -12 = FFFF\_FFF4 \ (in \ hex) \\ & -12/3 = FFFF\_FFF4 \ (in \ hex) \\ & -12/3 = FFFF\_FFFC \\ \hline regA = 'h1z; & regA = 001z & // regA \ is \ 16 \ bits. \ 'h1z = 0001\_zzzz, \ zero \ extended \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1ntA = -4 012 / 3; | 1000000000000000000000000000000000000 | -                                               |

| bit vector $-4'd12 = 2's$ complement of the 32-bit vector $= 2's$ complement(0000_000C) = FFFF_FF4 $-4'd12/3 = FFFF_FF4/3 = 5555_5551$ regA = -12 / 3regA = FFFC// -12 is an integer 32-bit number $-12 = FFFF_FF4$ (in hex) $-12/3 = FFFF_FFFC$ regA = 'h1z;regA = 001z//regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                                       |                                                 |

| $\begin{array}{ c c c c c c } & -4'd12 = 2's \ complement \ of \ the \ 32-bit \ vector \\ & = 2's \ complement(0000_000C) = FFFF_FF4 \\ & -4'd12/3 = FFFF_FF4/3 = 5555_5551 \\ \hline regA = -12 \ / \ 3 & regA = FFFC & // \ -12 \ is \ an \ integer \ 32-bit \ number \\ & -12 = FFFF_FF4 \ (in \ hex) \\ & -12/3 = FFFF_FF4 \ (in \ hex) \\ & -12/3 = FFFF_FFC \\ \hline regA = 'h1z; & regA = 001z & //regA \ is \ 16 \ bits. \ 'h1z = 0001_zzzzz, \ zero \ extended \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                       | -                                               |

| $= 2's \text{ complement}(0000\_000C) = FFFF\_FF4$ $-4'd12/3 = FFFF\_FF4/3 = 5555\_5551$ $regA = -12/3 \qquad regA = FFFC \qquad // -12 \text{ is an integer } 32-bit \text{ number}$ $-12 = FFFF\_FFF4 \text{ (in hex)}$ $-12/3 = FFFF\_FFFC$ $regA = 'h1z; \qquad regA = 001z \qquad //regA \text{ is } 16 \text{ bits. 'h1z} = 0001\_zzzz, \text{ zero extended}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                       |                                                 |

| $-4'd12/3 = FFFF_FF4/3 = 5555_551$ regA = -12 / 3regA= FFFC $// -12$ is an integer 32-bit number<br>$-12 = FFFF_FFF4$ (in hex)<br>$-12/3 = FFFF_FFFC$ regA = 'h1z;regA= 001z//regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                                       |                                                 |

| regA = -12 / 3regA= FFFC// -12 is an integer 32-bit number<br>$-12 = FFFF_FFF4$ (in hex)<br>$-12/3 = FFFF_FFFC$ regA = 'h1z;regA= 001z//regA is 16 bits. 'h1z = 0001_zzzz, zero extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                       | <b>A</b>                                        |