# **Component Design by Example**

... a Step-by-Step Process Using VHDL with UART as Vehicle

### **Ben Cohen**

VhdlCohen Publishing Los Angeles, California http://www.vhdlcohen.com

## **Component Design by Example**

... A Step-by-Step Process Using VHDL with UART as Vehicle

Published by:

VhdlCohen Publishing

P.O. 2362

Palos Verdes Peninsula CA 90274-2362

vhdlcohen@aol.com

http://www.vhdlcohen.com or

http://members.aol.com/vhdlcohen/vhdl/

Library of Congress Cataloging-in-Publication Data Library of Congress Card Number: 00-109498 Cohen, Ben Component Design by Example ISBN 0-9705394-0-1

Copyright © 2001 by VhdlCohen Publishing

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without the prior written permission from the author, except for the inclusion of brief quotations in a review.

Printed on acid-free paper

**Printed in the United States of America**

Preface

### **NOTES ADDED December 18, 2014**

This book was written in 2001. Since then technology has changed, and the verification methodologies have improved. Specifically, Verilog matured to become SystemVerilog and assertion languages matured along with formal verification. However,m VHDL did not make such pogress and in MHO, is lagging behind. Below are some of the changes that occured in SystemVerilog. However, I need to caution the readers of this book that the verification methodologies offered here are outdated and are not recommended. The guidelines in writing specifications and requirements still hold.

SystemVerilog supports specific features for verification, and those are not supported by VHDL. Several aspects are needed in verification:

- 1) Stimulus generator. For that SV supports:

- a) Constraint random generation with random gen stability. FYI, on random stability: This explains it <a href="http://www.testbench.in/CR\_20\_RANDOM\_STABILITY.html">http://www.testbench.in/CR\_20\_RANDOM\_STABILITY.html</a>

Basically, this deals with reproducability because of calls to RNG (random number generator (something not available in VHDL)

2) Verification of results:

This is supported by SystemVerilog Assertions (SVA) and by data structures needed for verification; these include associative arrays, queus, mailboxes, the generate statement (like VHDL), vectors.

- 3) Coverage to determine when done, or how much was done. SV provides the SVA cover and the covergroup to help in that respect.

- 4) flexibility for changes

SV has classes that can be extended and dynamically linked to other classes to accommodate changes and tests.

5) standards: UVM was developed to facilitate the standardization for the development of TBs.

I authored several books on VHDL and Verilog (which represents the RTL part of SystemVerilog) and to me, the two languages are pretty much similar, except for syntax. After being a very strong advocate of VHDL, I changed my beliefs and switched to SystemVerilog, even for just the Verilog subset of it. It is less restrictive, but requires good coding guidelines. I am also a very strong advocate of SystemVerilog assertions (SVA) because they help in the clarification of the requirements and in the debugging and verification process. Formal verification is

gaining wide acceptance, and uses SVA for the definitions of the properties of the design. I also like the UVM methodology and approaches, though UVM is not very straightforward, and requires care, with a good understanding of SystemVerilog. However, with some guidance and rules, I believe that one can effectively use UVM with a lesser than full understanding of SystemVerilog. What I am talking about it is the use of predefined templates for the basic building blocks.

-----

#### Ben Cohen

http://www.systemverilog.us/ben@systemverilog.us

- \* SystemVerilog Assertions Handbook 3rd Edition, 2013 ISBN 878-0-9705394-3-6

- \* A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- \* Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- \* Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- \* Component Design by Example ", 2001 ISBN 0-9705394-0-1

- \* VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- \* VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

\_\_\_\_\_\_

Preface

# **Contents**

| FORE<br>X  | EWORD                          | I  |

|------------|--------------------------------|----|

| a<br>PREF  | 'A CF                          |    |

|            | XI                             |    |

|            | UT THEXV                       |    |

| ACKN<br>II | NOWLEDGEMENTS                  | XV |

|            | UT THE<br>HORXIX               |    |

| DISCI      | LAIMER                         | XX |

| 1 0        | VERVIEW                        | 1  |

| 1.1        |                                |    |

|            |                                |    |

| 2 R        | EQUIREMENT SPECIFICATION       | 7  |

| 2.1        | Language                       | 8  |

| 2.2        | UART REQUIREMENT SPECIFICATION |    |

|            | 1.0 SCOPE                      |    |

|            | 1.1 SCOPE                      | 12 |

|            | 1.2 PURPOSE                    |    |

|            | 1.3 CLASSIFICATION             |    |

|            | 2.0 DEFINITIONS                |    |

|            | 2.1 ASYNCHRONOUS TRANSMISSION  |    |

|            | 2.2 BAUD RATE                  |    |

|            | 2.3 DTE                        |    |

|            | 2.4 DCE                        |    |

|            | 2.5 FRAMING ERROR              |    |

|            | 2.6 OVERRUN ERROR              |    |

|            | 2.7 PARITY                     |    |

|            | 2.8 START BIT<br>2.9 STOP BIT  |    |

|            | 2.10 SYNCHRONOUS TRANSMISSION  |    |

|            | 2.11 UNDERRUN ERROR            |    |

|            | 2.12 WORD (WITH UART)          |    |

|            | 3.0 APPLICABLE DOCUMENTS       |    |

|   | 3.1 GOVERNMENT DOCUMENTS       |          |

|---|--------------------------------|----------|

|   | 3.2 NON-GOVERNMENT DOCUMENTS   |          |

|   | 3.3 EXECUTABLE SPECIFICATIONS  |          |

|   | 4. 0 ARCHITECTURAL OVERVIEW    |          |

|   | 4.1 INTRODUCTION               |          |

|   | 4.2 SYSTEM APPLICATION         |          |

|   | 5.0 PHYSICAL LAYER             |          |

|   | 5.1 INTERFACE PORT DESCRIPTION |          |

|   | 6.0 PROTOCOL LAYER             |          |

|   | 7.0 ROBUSTNESS                 |          |

|   | 7.1 ERROR DETECTION            |          |

|   | 8.0 HARDWARE AND SOFTWARE      |          |

|   | 8.1 FIXED PARAMETERIZATION     |          |

|   | 8.2 SOFTWARE INTERFACES        |          |

|   | 8.3 MODES OF OPERATION         |          |

|   | 9. 0 PERFORMANCE               |          |

|   | 9.1 FREQUENCY                  |          |

|   | 9.2 POWER DISSIPATION          |          |

|   | 9.3 ENVIRONMENTAL              |          |

|   | 9.4 TECHNOLOGY                 | 30       |

|   | 10.0 TESTABILITY               | 30       |

|   | 11.0 MECHANICAL                | 30       |

| 3 | ARCHITECTURAL PLAN             |          |

|   | 1.0 SCOPE                      |          |

|   | 1.1 SCOPE                      |          |

|   | 1.2 PURPOSE                    |          |

|   | 1.3 CLASSIFICATION             |          |

|   | 2.0 DEFINITIONS                |          |

|   | 3.0 APPLICABLE DOCUMENTS       |          |

|   | 4.0 ARCHITECTURAL OVERVIEW     |          |

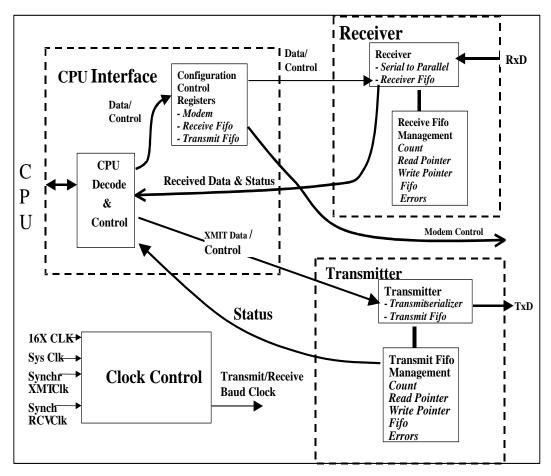

|   | 4.1 CPU SUBBLOCK               |          |

|   | 4.2 RECEIVER SUBBLOCK          |          |

|   | 4.3 TRANSMIT SUBBLOCK          |          |

|   | 4.4 CLOCK SUBBLOCK             |          |

|   | 5.0 PHYSICAL LAYER             |          |

|   | 6.0 PROTOCOL LAYER             |          |

|   | 7.0 ROBUSTNESS                 |          |

|   | 8.0 HARDWARE AND SOFTWARE      | 37       |

|   | 8.1 FIXED PARAMETERIZATION     |          |

|   |                                |          |

|   | 8.2 SOTWARE INTERFACES         |          |

|   | 9.0 PERFORMANCE                | 37<br>37 |

|   |                                | 37<br>37 |

|   | VERI                                                                  | FICATION PLAN                                                                                                                                                                                                                                                  | 39                               |

|---|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 4.1 M                                                                 | ETHODOLOGIES                                                                                                                                                                                                                                                   | 40                               |

|   | 4.1.1                                                                 | What is a Verification Plan                                                                                                                                                                                                                                    |                                  |

|   | 4.1.2                                                                 | Why a Verification Plan.                                                                                                                                                                                                                                       |                                  |

|   | 4.1.3                                                                 | Verification Languages                                                                                                                                                                                                                                         |                                  |

|   |                                                                       | ERIFICATION PLAN                                                                                                                                                                                                                                               |                                  |

|   |                                                                       | COPE                                                                                                                                                                                                                                                           |                                  |

|   |                                                                       | 1.1 SCOPE                                                                                                                                                                                                                                                      |                                  |

|   |                                                                       | 1.2 PURPOSE                                                                                                                                                                                                                                                    |                                  |

|   |                                                                       | 1.3 CLASSIFICATION                                                                                                                                                                                                                                             |                                  |

|   |                                                                       | DEFINTIONS                                                                                                                                                                                                                                                     |                                  |

|   |                                                                       | PPLICABLE DOCUMENTS                                                                                                                                                                                                                                            |                                  |

|   |                                                                       | 3.1 GOVERNEMENT DOCUMENTS                                                                                                                                                                                                                                      | 48                               |

|   |                                                                       | 3.2 NON-GOVERNEMENT DOCUMENTS                                                                                                                                                                                                                                  |                                  |

|   |                                                                       | 3.3 EXECUTABLE SPECIFICATIONS                                                                                                                                                                                                                                  |                                  |

|   |                                                                       | 3.4 REFERENCE SOURCES                                                                                                                                                                                                                                          | 48                               |

|   |                                                                       | OMPLIANCE PLAN                                                                                                                                                                                                                                                 |                                  |

|   | 4                                                                     | 4.1 FEATURE EXTRACTION AND TEST STRATEGY                                                                                                                                                                                                                       | 49                               |

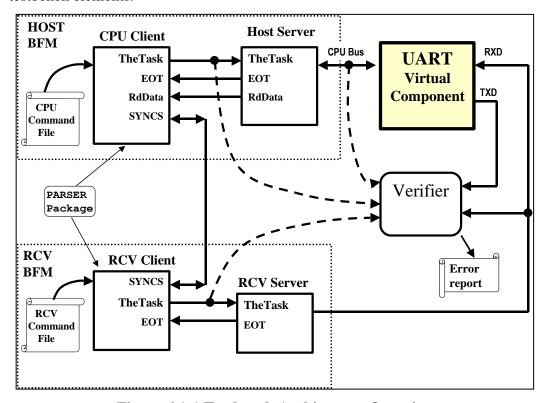

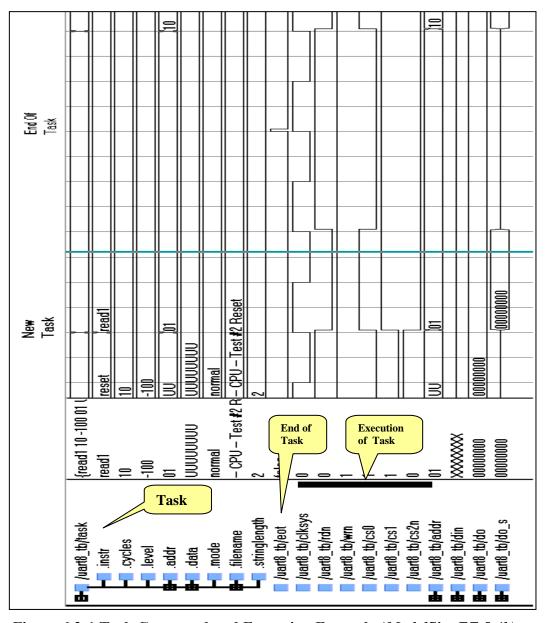

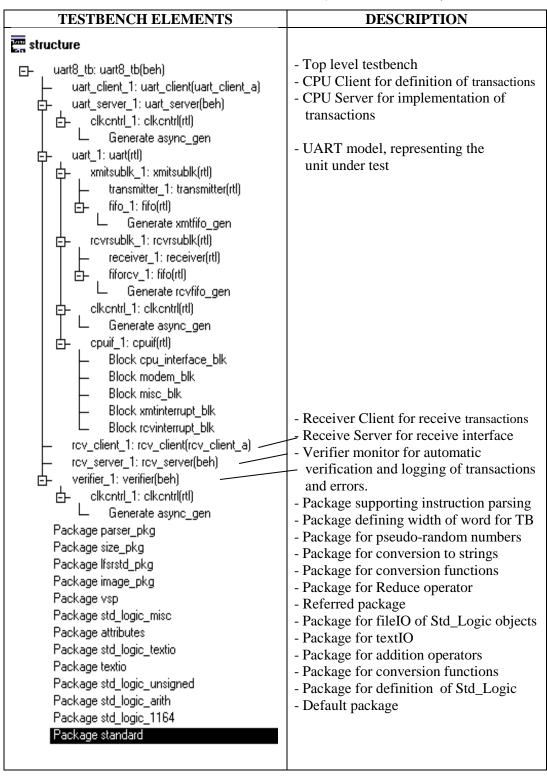

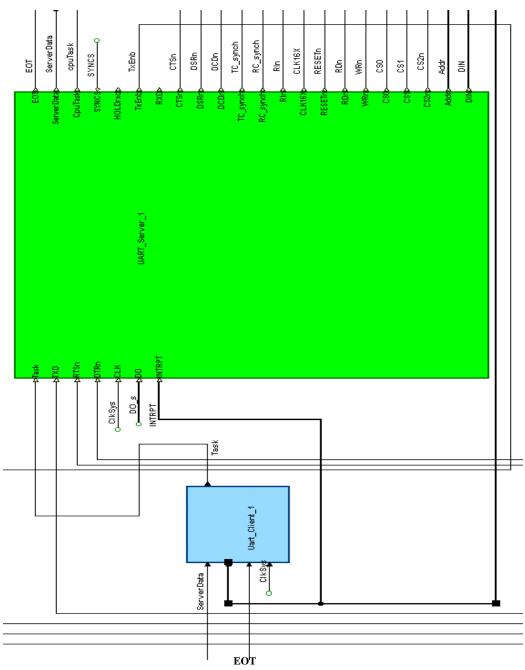

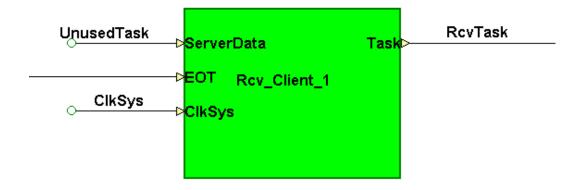

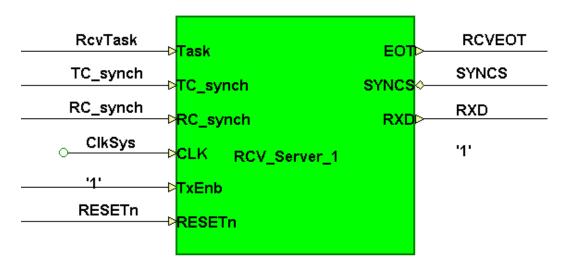

|   |                                                                       | 4.2 TESTBENCH ARCHITECTURE                                                                                                                                                                                                                                     |                                  |

|   | 4                                                                     | 4.3 VERIFIER                                                                                                                                                                                                                                                   | 69                               |

|   | 5. Di                                                                 | ESIGN TOOLS                                                                                                                                                                                                                                                    | 72                               |

|   |                                                                       |                                                                                                                                                                                                                                                                |                                  |

| 5 | DESIG                                                                 | GN AND SYNTHESIS                                                                                                                                                                                                                                               | 73                               |

| 5 |                                                                       |                                                                                                                                                                                                                                                                |                                  |

| 5 |                                                                       | ΓL DESIGN                                                                                                                                                                                                                                                      | 73                               |

| 5 | 5.1 R                                                                 |                                                                                                                                                                                                                                                                | 73<br>74                         |

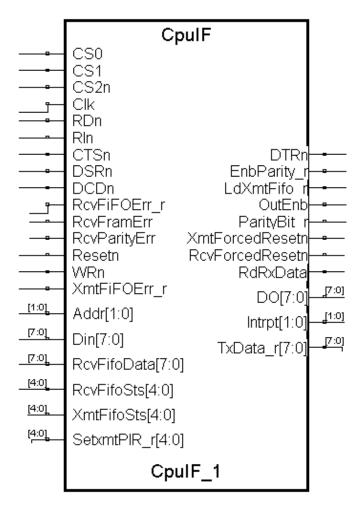

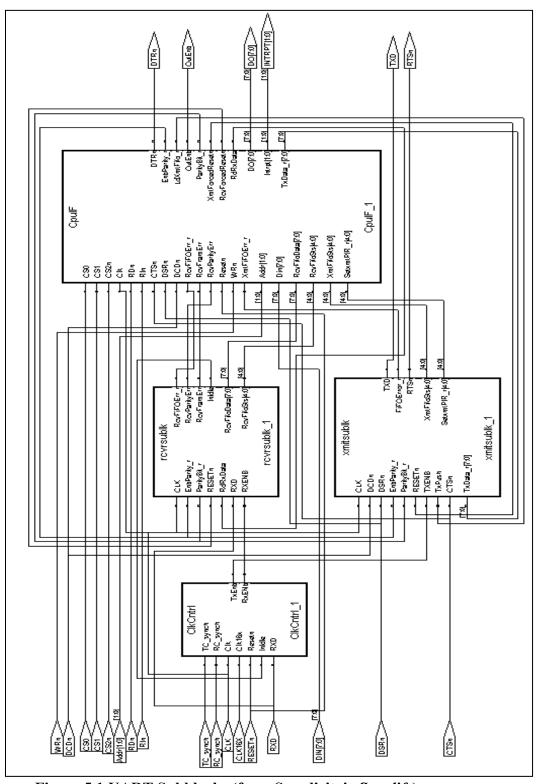

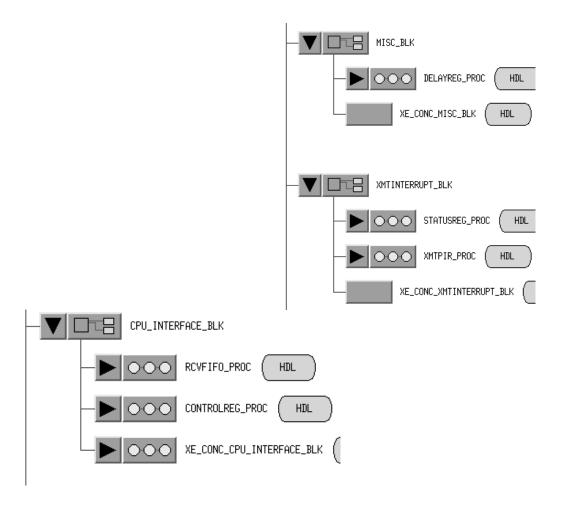

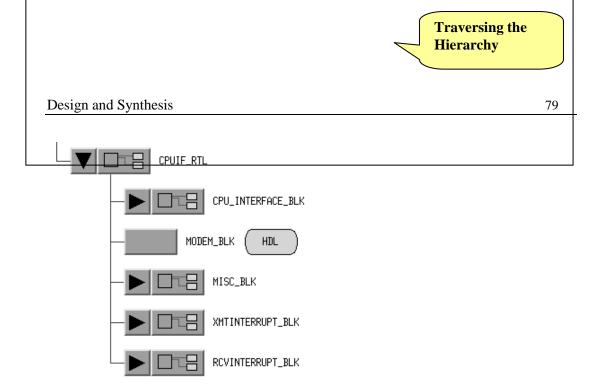

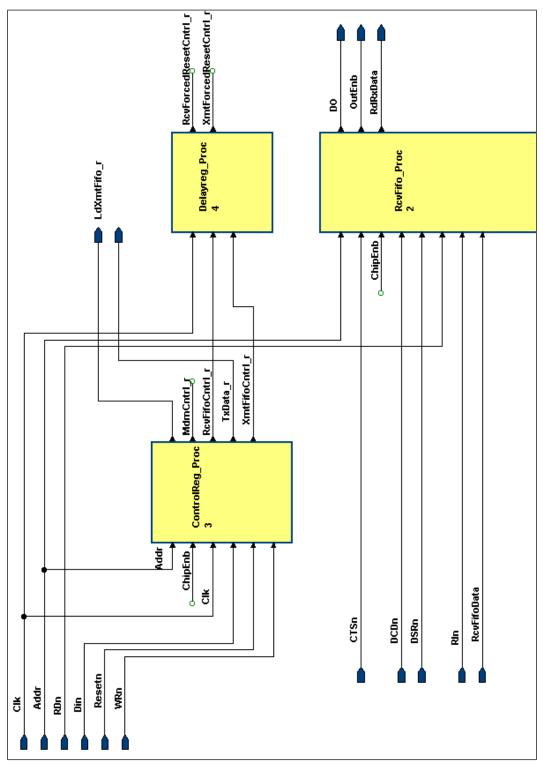

| 5 | 5.1 R7<br>5.1.1                                                       | TL DESIGN  CPU Interface (CpuIf) Subblock Design                                                                                                                                                                                                               | 73<br>74<br>84                   |

| 5 | 5.1 R                                                                 | TL DESIGN CPU Interface (CpuIf) Subblock Design                                                                                                                                                                                                                | 73<br>74<br>84<br>91             |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2                                              | TL DESIGN  CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD                                                                                                                                                                       | 73<br>84<br>91<br>93             |

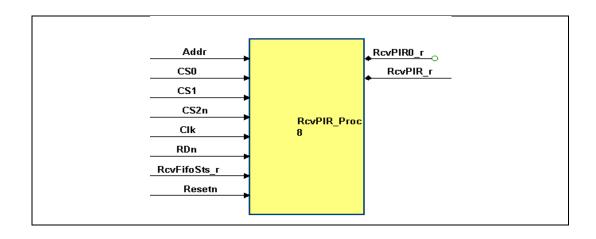

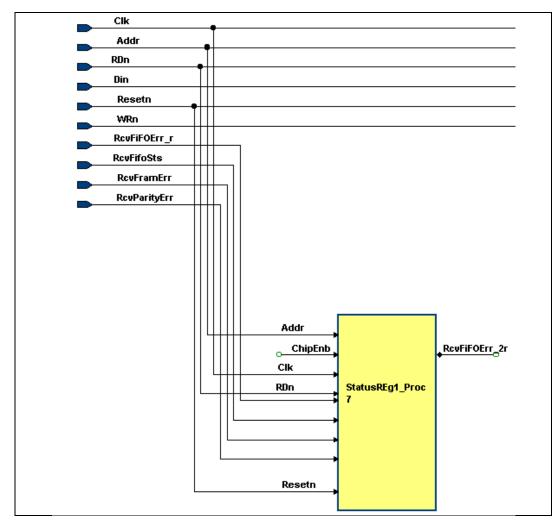

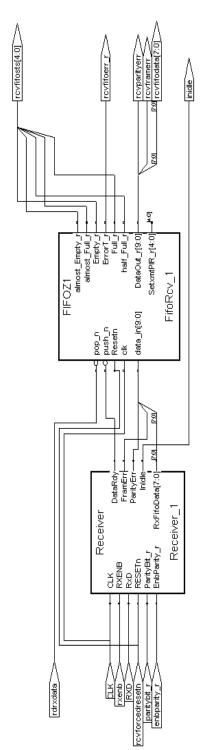

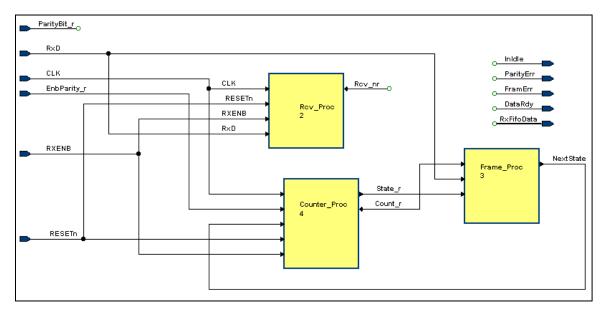

| 5 | 5.1 R7<br>5.1.1                                                       | TL DESIGN  CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)                                                                                                                                         | 73<br>                           |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2                                              | TL DESIGN  CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD                                                                                                                                                                       | 73<br>74<br>84<br>91<br>93<br>95 |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2                                              | TL DESIGN  CPU Interface (CpuIf) Subblock Design                                                                                                                                                                                                               |                                  |

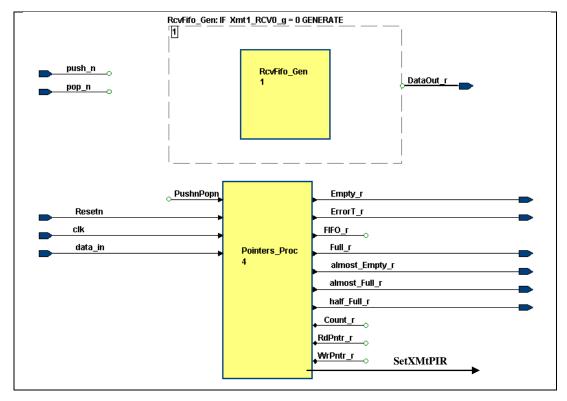

| 5 | 5.1 R7<br>5.1.1<br>5.1.2                                              | TL DESIGN  CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD                                                                                                   |                                  |

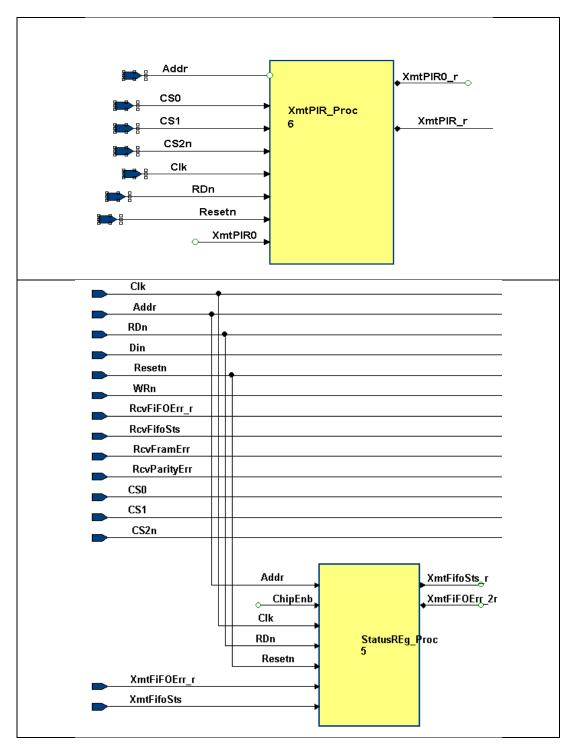

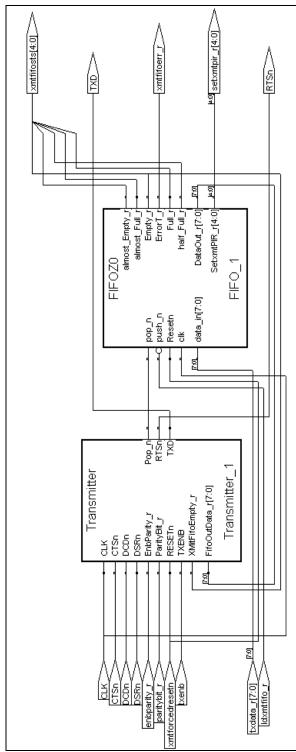

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3                                     | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)                                                                               |                                  |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3                                     | TL DESIGN  CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD                                                                                                   |                                  |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3                                     | TL DESIGN  CPU Interface (CpuIf) Subblock Design                                                                                                                                                                                                               |                                  |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3                                     | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)  UART Model  XMITSUBLK.VHD                                                    |                                  |

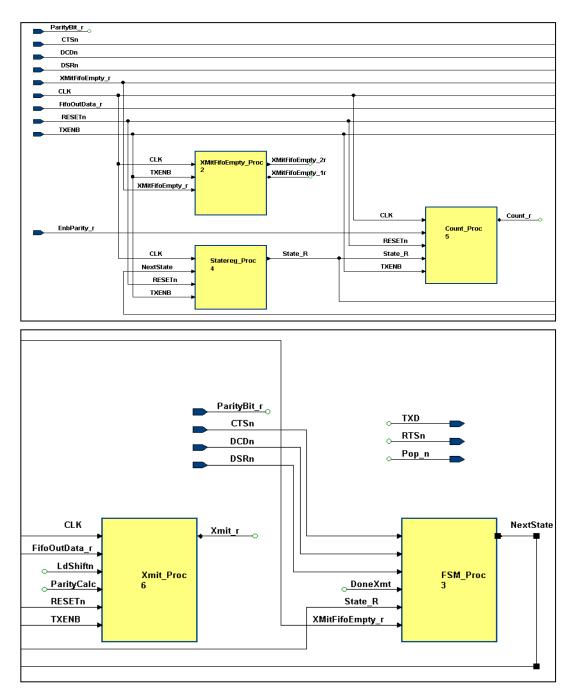

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3                                     | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)  UART Model  XMITSUBLK.VHD  TRANSMITTER.VHD                                   |                                  |

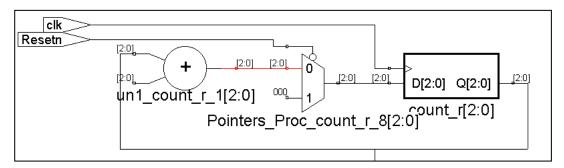

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                   | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)  UART Model  XMITSUBLK.VHD  TRANSMITTER.VHD  UART.VHD  UART.VHD  Compilation  |                                  |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7 | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)  UART Model  XMITSUBLK.VHD  TRANSMITTER.VHD  UART.VHD  Compilation  Synthesis |                                  |

| 5 | 5.1 R7<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                   | CPU Interface (CpuIf) Subblock Design  CPUIF.VHD  Clock Control  CLKCNTRL.VHD  Receiver Subblock (rcvsublk)  RCVSUBLK.VHD  RECEIVER.VHD  FIFO.VHD  Transmit Subblock (xmitsublk)  UART Model  XMITSUBLK.VHD  TRANSMITTER.VHD  UART.VHD  UART.VHD  Compilation  |                                  |

| 6 | DE         | SIGN VERIFICATION                                            | 131 |

|---|------------|--------------------------------------------------------------|-----|

|   | 6.1        | OVERVIEW                                                     | 132 |

|   | 6.2        | PARSER PACKAGE                                               | 132 |

|   |            | PARSER_PB.VHD                                                | 135 |

|   | 6.3        | CLIENT MODEL                                                 | 144 |

|   |            | UART_CLIENTRNDM.VHD                                          | 147 |

|   |            | RCV_CLIENT.VHD                                               |     |

|   | 6.4        | Server                                                       |     |

|   |            | UART_SERVER.VHD                                              |     |

|   |            | RCV_SERVER.VHD                                               |     |

|   |            | FIFO_SERVER.VHD                                              |     |

|   | - <b>-</b> | FIFO_TB.VHD                                                  |     |

|   | 6.5        | VERIFIER                                                     |     |

|   | 6.5.       |                                                              |     |

|   | 6.5.2      | $\mathcal{E}$                                                |     |

|   | 6.5.       |                                                              |     |

|   | 6.5.4      | 1                                                            |     |

|   | 6.5.       | $\mathcal{C}$                                                |     |

|   |            | VERIFPEEK.VHD                                                |     |

|   |            | UART8_TB.VHD                                                 |     |

|   | <i></i> .  | UART_C.VHD                                                   |     |

|   | 6.5.0      |                                                              |     |

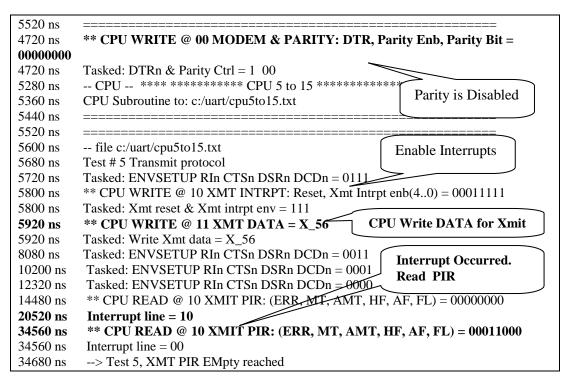

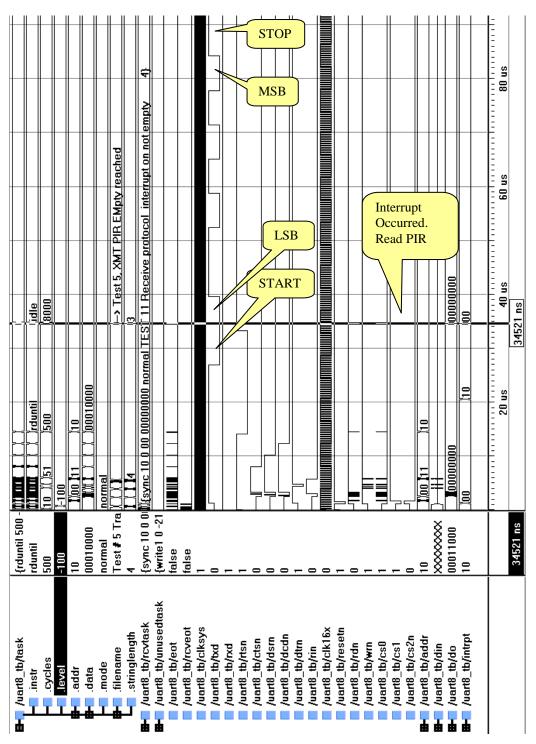

|   |            | COMMAND FILE: INSTR1.TXTCOMMAND FILE: CPU5TO15.TXT           |     |

|   |            | COMMAND FILE: CPUSIOIS.TXT                                   |     |

|   |            | COMMAND FILE: SW_KESET.TXT                                   |     |

|   |            | COMMAND FILE: RCV11TO15.TXT                                  |     |

|   | 6.5.       |                                                              |     |

|   | 6.5.8      | 1                                                            |     |

|   | 6.5.9      |                                                              |     |

| 7 |            | CUMENTATION AND DELIVERY                                     |     |

|   | 2.1        | Introduction                                                 | 234 |

|   | 2.2        | REFERENCE INFORMATION                                        | 234 |

|   | 2.2.       | Documented References                                        |     |

|   | 2.2.2      | 2 Terminology                                                | 234 |

|   | 2.3        | DELIVERABLE OVERVIEW                                         |     |

|   | 2.4        | DATA ORGANIZATION FOR THE PACKAGING OF DELIVERABLES          |     |

|   | 2.5        | DELIVERABLES DESCRIPTIONS                                    |     |

|   | 2.5.       |                                                              |     |

|   | 2.5.       |                                                              |     |

|   | 2.5.       |                                                              |     |

|   | 2.5.4      |                                                              |     |

|   | 2.5.5      |                                                              |     |

|   | 2.5.       | , e                                                          |     |

|   | ۷.٥.۵      | Design-tor-test and ivialidiaciding-Kerated Test Denverables | 448 |

Preface ix

|   | 2.5.7                                               | Functional Verification Deliverables                                                                                          | 248                      |

|---|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 2.5.8                                               | Design Analysis Deliverables                                                                                                  |                          |

|   |                                                     | SIGN STATUS AND RECOMMENDATIONS                                                                                               |                          |

|   | 2.6.1                                               | Status                                                                                                                        |                          |

|   | 2.6.2                                               | Suggested Work                                                                                                                |                          |

|   | 2.7 OP                                              | ENMORE                                                                                                                        |                          |

| 8 | INTEG                                               | GRATION OF COMPONENTS INTO DESIGNS                                                                                            | 263                      |

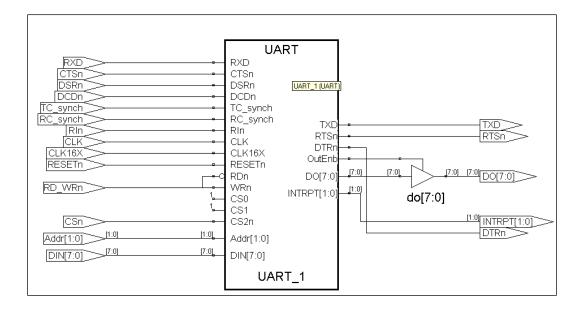

|   | 8.1 AP                                              | PLICATION OF UART INTO HIGHER LEVEL DESIGN                                                                                    | 264                      |

|   |                                                     | UART_LEVEL2.VHD                                                                                                               | 265                      |

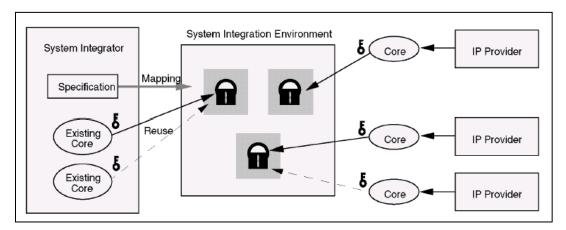

|   |                                                     | GHER LEVEL COMPONENT EXTRACTION AND INTEGRATION                                                                               |                          |

|   | 8.2.1                                               | Motivation for change                                                                                                         |                          |

|   | 8.2.2                                               | Related Industry Trends                                                                                                       |                          |

|   | 8.2.3                                               | Types of IP Cores Error! Bookmark I                                                                                           |                          |

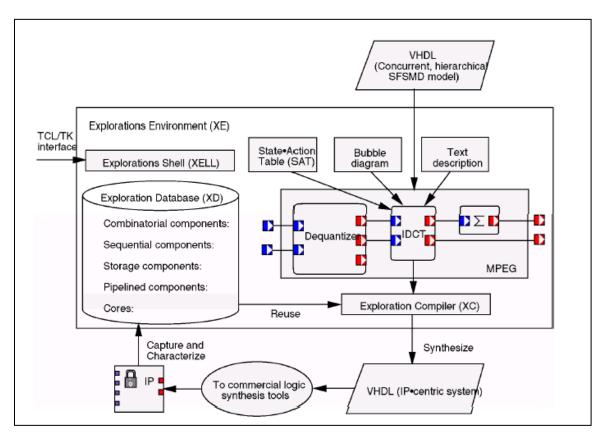

|   | 8.2.4                                               | Reuse Automation through High-Level Synthesis                                                                                 |                          |

|   | 8.2.5<br>8.2.6                                      | IP-Centric Synthesis Methodology Summary and Recommendation Error! Bookmark I                                                 |                          |

| 9 | REFLI                                               | ECTIONS                                                                                                                       | 276                      |

|   | 9.1 RE                                              | QUIREMENTS                                                                                                                    | 276                      |

|   | 9.1.1                                               | Realities                                                                                                                     | 27.0                     |

|   | 9.1.2                                               |                                                                                                                               | 276                      |

|   | 9.1.3                                               | System implications                                                                                                           | 278                      |

|   |                                                     | Consistency                                                                                                                   | 278<br>279               |

|   |                                                     | Consistency                                                                                                                   | 278<br>279<br>280        |

|   | 9.3 VE                                              | Consistency                                                                                                                   | 278<br>279<br>280        |

|   | 9.3 VE<br>9.3.1                                     | Consistency SIGN RIFICATION Value of verifier                                                                                 | 278<br>279<br>280<br>281 |

|   | 9.3 VE<br>9.3.1<br>9.3.2                            | Consistency                                                                                                                   | 278279280281282          |

|   | 9.3 VE<br>9.3.1<br>9.3.2<br>9.3.3                   | Consistency SIGN RIFICATION Value of verifier Code coverage Debugger/LINTing                                                  |                          |

|   | 9.3 VE<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4          | Consistency SIGN RIFICATION Value of verifier Code coverage Debugger/LINTing When is design fully verified                    |                          |

|   | 9.3 VE<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5 | Consistency SIGN RIFICATION Value of verifier Code coverage Debugger/LINTing When is design fully verified Text Command Files |                          |

|   | 9.3 VE<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4          | Consistency SIGN RIFICATION Value of verifier Code coverage Debugger/LINTing When is design fully verified                    |                          |

|   | 9.3 VE<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5 | Consistency SIGN RIFICATION Value of verifier Code coverage Debugger/LINTing When is design fully verified Text Command Files |                          |

### **FOREWORD**

When Ben first asked me if I would be interested in reviewing his latest book, I was dually thrilled; once for the opportunity to contribute to the subject matter, second because it meant that Ben was taking on some new issues. In my many years with Synplicity®, I have had the opportunity to read or review many books. Of those, very few I appreciated enough to recommend. Two of Ben's earlier books, VHDL Coding Styles and Methodologies and VHDL Answers to Frequently Asked Questions are truly the best of the lot. They have long been on my technical recommendation list. Ben has an academic knowledge of the VHDL language, but utilizes that information with a practitioner's sense of reason. Both of these works are targeted toward the designer who utilizes VHDL. He fills these books with tips and recommendations, explanations as to why decisions are made and many references for further reading. What we gain from these books are a practical guide to applying VHDL with consideration for both the circuits to be implemented as well as the tools that you will used to create and verify the designs. I was anticipating that this new work would be similar in approach.

In Component Design by Example, Ben attacks the design reuse problem. This topic is timely and important. The Electronic Design Automation community has spent the most of the last decade foreshadowing the emergence and importance of design re-use and "IP" to obtain the next level of productivity gains. It is only in recently that we have seen more frequent occurrences of design reuse. In the past few years, our customers have begun to utilize various sizes and complexities of IP. With our customers, we have discussed, planned, pondered and solved various problems and futures for the development and reuse of design data and modular design flows. Consequently, we have observed that there is much design data that is reused, but only after significant effort. Often this is because the module was not successfully designed with reuse in mind. I suspect that many designers lacked resources and references broad enough to be useful on the topic of design for reuse.

Preface

Ben has created a pragmatic and useful book on design for reuse. It is useful because it brings lots of practical information and experience in one place. Useful because he dares to go beyond just the implementation phases of design, (which is more frequently addressed), and takes on the procedures from conception to specification and planning. PLEASE DON'T DISMISS THESE SECTIONS! Too many projects get into too much trouble down the line due to incomplete, ambiguous, or "undocumented" specifications and inadequate planning. It seems obvious, yet so many designers think of it as overhead that impedes progress.

Component Design by Example will be useful to any designer or design team. It may improve efficiency and improve products, or create disagreement in approach. My hope is it will stimulate discussion. I expect it will be the foundation for a future filled with IP. Read this before your next project. Then reread it afterward. You will benefit both times.

Andrew R. Dauman Vice-President of Corporate Applications Synplicity, Inc. Sunnyvale, CA September 28, 2000

### **PREFACE**

As a VHDL trainer, consultant, and designer I recognized the need to demonstrate how to organize designs from conception to verified products. Many books address the design processes that include reuse methodologies for components, subblocks, and ASIC/FPGA designs. Since 1996, the *Virtual Socket Interface Alliance* TM (VSIA) has played a key role in the design reuse scenario by creating standards for the industry that permits even broader reuse. These books and standards provide guidelines and general recommendations, but lack the provisions of complete design examples (with code) that demonstrate all the front-end phases of a design process. These phases include definition of requirements, architecture, verification approaches, HDL coding, synthesis, verification, and documentation. This book covers this gap and addresses the process of defining requirements and translating these requirements into a verified soft component design.

A component is taken in the sense of a design unit, subblock (or partition of a larger design), and a commercial Intellectual Property (IP). This book recognizes that there are many methodologies adopted by industry to perform front-end designs. This book provides methodologies generally accepted and recommended by many textbooks, including: *Reuse Methodology Manual*, Michael Keating and Pierre Bricaud, *Writing Testbenches, Functional verification of HDL Models*, Janick Bergeron, and *Verification Methodology Manual for Code Coverage in HDL Designs* by Michael Stuart and David Dempster. Users can tailor their methodologies to what is required given the constraints of labor force, budgets, and available tools. Even though tools do not represent methodologies, tools are often used to guide methodologies.

This book serves the following goals:

- 1. It demonstrates, by example, the **processes** involved in specifying, implementing, and verifying a reusable soft component. Most of these front-end processes are independent of the HDL implementation or verification languages. Even though the disciplines involved in every project and company will vary, the presented processes provide a good modeling base that users can modify and build upon. This is the focus and purpose of the book.

- 2. It demonstrates how to write a **requirement specification** that defines the foundation of the design. Defining a good specification is a difficult task

<sup>&</sup>lt;sup>1</sup> Virtual Socket Interface Alliance TM http://www.vsi.org

Preface

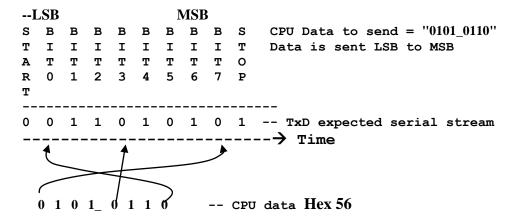

as no single approach represents an exclusive best solution. It discusses potential specification methodologies, and provides a subset of this domain space as a modeling example to specify a serial interface, which is **UART-like in requirements**. These requirements meet those defined in the EIA (Electronics Industry Association) standard for serial data communication RS-232 UART. To emulate the challenges of real designs, such as parameterization and adaptability to different modes, this design adds additional performance requirements including: word widths, storage depths, and interrupt controller. This UART design is a soft component vehicle, and represents a model of moderate complexity with adaptability to many applications. A UART is a Universal Asynchronous Receiver Transmitter.

- 3. It demonstrates how to write an **architectural implementation** document, before writing any HDL code. This document defines the architectural approach for analysis and review.

- 4. It demonstrates how to write reusable and parameterized **VHDL synthesizable RTL code** for designs *using IEEE 1076.6 VHDL RTL for synthesis guidelines*<sup>2</sup>. This parameterization emulates typical components that require such flexibilities.

- 5. It demonstrates how to write a **verification plan** that defines the foundation of the verification approaches of a design. This document is essential because it guides the design of the testbench and verification models, and provides a forum for scrutinizing the validity and completeness of the tests.

- 6. It demonstrates how to verify a design using **reusable testbenches in VHDL**.<sup>3</sup> The issues of verification techniques are quite controversial,<sup>4</sup> particularly with the advent of new verification tools and languages. The elementary concepts of verification are independent of tools or languages, even though tools and languages are used to implement the verification. This book concentrates on the strict use of VHDL as the verification language because it is opened and portable. It illustrates advanced VHDL modeling techniques for the generation of stimulus vectors, including the use of text command files, client/server models, and pseudo-random transactions. The text commands for the control of transactions include a rich, but small, instruction set capable to recursively call command files defined as subroutines.

- 7. It demonstrates the design and synthesis process, including results of synthesis and post-route with Altera tools.

<sup>3</sup> Those techniques are referenced in the following books: VHDL Coding Styles and Methodologies, 2<sup>nd</sup> Edition, Ben Cohen, KAP, 1999. Writing Testbenches: Functional Verification of HDL Models, Janick Bergeron, KAP 2000

<sup>&</sup>lt;sup>2</sup> See http://www.vhdl.org/siwg

<sup>&</sup>lt;sup>4</sup> See http://janick.bergeron.com/guild

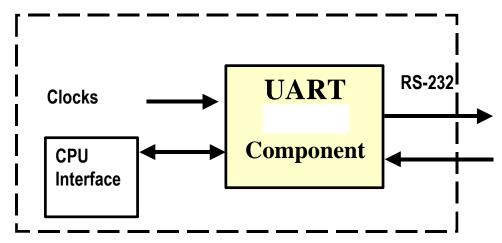

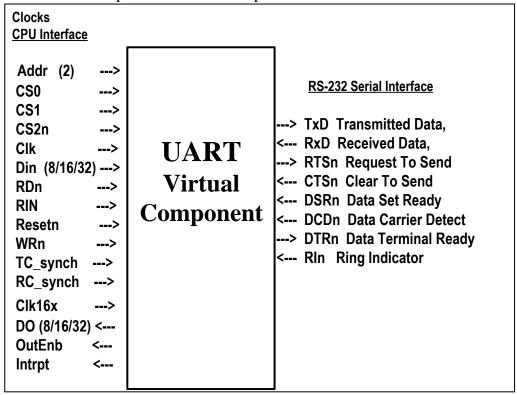

- 8. It provides, as a by-product of these methodologies, the design of a **high-speed**, **full-featured UART-like soft component** that can be tailored to applications that require an asynchronous or synchronous serial 8, 16, and 32-bit interface between two equipments.

- 9. It demonstrates the **integration of the soft component** into a subsystem.

- 10. It demonstrates the filling of the **OpenMore spreadsheet**. OpenMore is an assessment program developed by Synopsys and Mentor Graphics designed to enable a self-assessment of the reusability of commercial IP offerings.

- 11. It demonstrates an application of a *Virtual Component Block Deliverables* document, as described by *Motorola's Semiconductor Reuse Standard*<sup>5</sup>.

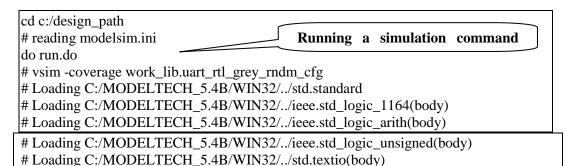

All VHDL code described in the book is on a companion CD. All code was verified and simulated with *ModelSim version 5.4b*,<sup>6</sup> and synthesized with *Synplify* version 5.3.1.<sup>7</sup> The CD also includes the **GNU toolsuite** with **EMACS** language sensitive editor (with VHDL, Verilog, and other language templates), and **TSHELL** tools that emulate a Unix shell.

#### This book is intended for:

- 1. **Engineers.** Book provides examples for the processes involved in defining components from requirements through verification and synthesis. It represents templates for the definition and implementation of a design. Engineers are better at copying and improving upon what is done, than from starting from scratch. This book will provide a head start in these processes.

- 2. **Application Designers**. Engineers who need a UART can use or modify the models described in this book.

- 3. **Tool Developers.** This book defines a well-specified and documented model of a common design of medium complexity, with hierarchy. Tool developers may exercise these requirements and HDL designs through new tools to demonstrate enhancements in the design processes.

- 4. **Trainers.** This book provides the focus of an advanced class for the definition and application of front-end methodologies and processes.

- 5. College students. Book demonstrates the design processes, from

5 Motorola: http://www.mot-sps.com/technology/srs/index.html

Model Technology: http://www.model.com

Synplicity http://www.synplicity.com

Preface

requirements to a verified implementation. It models real working industry design experiences

This book will be helpful as a guide through all the phases of a front-end design. It provides useful document templates for the definition of the requirement, implementation, and test plan documents. It also provides reusable code for the design of testbenches, and demonstrates by example, the application of this code for the synthesis and verification of a UART model.

# **About The Disk**

Table 1 summarizes the contents of the enclosed CD.

**Table 1 Contents of Enclosed CD**

| DIRECTOR   | DESCRIPTION                                                       |  |

|------------|-------------------------------------------------------------------|--|

| YNAME      |                                                                   |  |

| vhdl/rtl   | clkcntrl.vhd clock controller subblock                            |  |

|            | cpuif.vhd CPU Interface subblock                                  |  |

|            | fifo.vhd FIFO subblock                                            |  |

|            | rcvsublk.vhd – Receiver top-level with receiver subblock and FIFO |  |

|            | receiver.vhd – Receiver subblock                                  |  |

|            | transmitter.vhd Transmitter subblock                              |  |

|            | xmitsublk.vhd top-level with transmitter subblock and FIFO        |  |

|            | uart.vhd UART, top-level                                          |  |

|            | uart_level2.vhd – integration of UART into higher level           |  |

| vhdl/tb    | vsp.vhd miscellaneous package                                     |  |

|            | lfsrstd.vhd Linear feedback shift register package                |  |

|            | image_pb.vhd image package for conversion to strings              |  |

|            | size_pkg.vhd – For testbench use, global signals and constants    |  |

|            | parser_pb.vhd – Parser package for file I/O and command parsing   |  |

|            | uart_server.vhd UART Server for TB                                |  |

|            | rcv_client.vhd Client for receive side of UART                    |  |

|            | rcv_server.vhd Server for receive side of UART                    |  |

|            | verifierpeek.vhd Verifier with use of global signals for synch    |  |

|            | verifierblkbox.vhd Verifier, black box approach                   |  |

|            | uart_clientrndm.vhd – Uart client with good random tests          |  |

|            | uart_client_bad.vhd Uart client with tests that produce errors    |  |

|            | uart8_tb.vhd Top level testbench for UART                         |  |

|            | uart_c.vhd Configuration declarations for UART testbench          |  |

|            | fifo_server.vhd Fifo server for use with uart client              |  |

|            | fifo_tb.vhd fifo testbench                                        |  |

|            | filedata.vhd Reading data from a file through linked lists        |  |

| vhdl/gates | uart.vho gate level model produced by Altera                      |  |

Preface xvii

| Directory   | Description                                                        |  |  |

|-------------|--------------------------------------------------------------------|--|--|

| Name        |                                                                    |  |  |

| uart        | cpu5to15.txt CPU subroutine command file                           |  |  |

|             | instr1.txt CPU command file                                        |  |  |

|             | rcv11to15.txt Receive side subroutine command file                 |  |  |

|             | rcvinstr.txt Receive side command file                             |  |  |

|             | sw_reset.txt Reset subroutine command file                         |  |  |

| scripts     | compile.do ModelSim compile scripts                                |  |  |

|             | compile.log – ModelSim compile log                                 |  |  |

|             | run.do ModelSim run simulation                                     |  |  |

| Altera      | Synplify EDIF files, Files produced by Altera                      |  |  |

| simRuns     | Gate_Sim – gate level simulation run output                        |  |  |

|             | RTL_BlkBox RTL black box simulation run output                     |  |  |

|             | RTL_GreyBoxRdmn RTL Gray box simulation run output                 |  |  |

|             | RTL_Grey_OverrunError – RTL Gray box with errors                   |  |  |

| IEEE        | NUMBIT.VHD, NUMSTD.VHD, STDLOGIC.VHD packages                      |  |  |

| Synopsys    | attribut.vhd, bvarith.vhd, slmisc.vhd, stdarith.vhd, stdtxtio.vhd, |  |  |

|             | std_cmpt.vhd, std_sign.vhd, std_unsg.vhd, synopsys.vhd packages    |  |  |

| modelsim_   | PLI for ModelSim to access signals internal to a design            |  |  |

| spy         |                                                                    |  |  |

| motorola_   | srsmotdeliverable.pdf Motorola deleiverable document template      |  |  |

| Deliverable |                                                                    |  |  |

| openMore    | openmore-uart.xls – OpenMore spreadsheet for UART                  |  |  |

|             | openmore.xls OpenMore spreadsheet unfilled                         |  |  |

| VHDL_       | VHDL'87 and VHDL'93 syntax in HTML format                          |  |  |

| Syntax      | VHDL Help: VHDL Language Reference Guide                           |  |  |

| Verilog     | CummingsSNUG2000SJ_NBA_rev1a.pdf,                                  |  |  |

|             | VerilogHDLCoding_Motorola.pdf, verilog_vs_vhdl.PDF,                |  |  |

|             | vlog1364- HDLCON-2000.pdf                                          |  |  |

| PDF_FIles   | ModelSIm5_2 reference guide, VHDL and Verilog reference cards,     |  |  |

|             | Std_Logic_1164 reference card, and European Space Agency           |  |  |

|             | Modeling guidelines                                                |  |  |

| Usr         | GNU toolset                                                        |  |  |

| man         | GNU help files in Windows Help format. Root file is ManPagesDir    |  |  |

| Etc         | Csh.cshrc and my.cshrc startup files for TSHEL                     |  |  |

## Acknowledgements

Component Design by Example evolved from the recent recognition in books, technical articles, and presentations on the need to follow a process for large designs. In particular, I thank Michael Keating, author of Reuse Methodology Manual, and, Janick Bergeron, author of Writing Testbenches, Functional verification of HDL Models and organizer of the Verification Guild newsletter for bringing forward those important design issues.

I thank Model Technology for granting me a license of *ModelSim version 5.4b* with the built-in code coverage for the duration of the project. *ModelSim* is an excellent user-friendly HDL toolset that enabled the compilation and verification of this design.

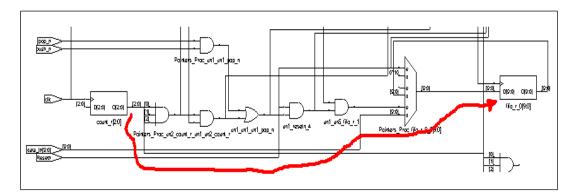

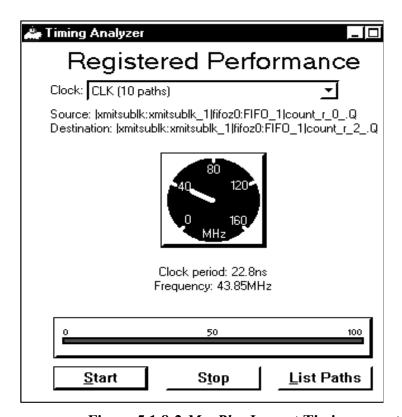

I thank Synplicity for granting a license of *Synplify HDL Analyst* version 5.3.1 to synthesize the design and to extract the RTL views and delay paths for visual display and documentation of the logic and critical paths. *Synplify is* a very efficient, user-friendly, and insightful linting FPGA synthesis tool.

Altera's MAX+PLUS® II ver 9.4 complemented Synplify's EDF output because it routed the design and produced an accurate gate level model with routed timing. Altera was kind enough to grant me a tool license for this project.

I thank Novas for granting me a license of *Debussy 5.0* Total Debug (tm) system for complex designs at the gate, RTL and behavioral levels. Even though the license came in late in the project, I was still able to gain insightful views of the design and testbench.

I thank Reto Zimmermann from Synopsys for commenting on the manuscript, and for supporting the community on the excellent upgrades to *vhdl-mode* for *emacs* GNU text editor. The application of the language sensitive *vhdl-mode* significantly helped in the production of VHDL code for design and verification.

I thank YxI for providing me with more insights into advanced synthesis methodologies from higher-level HDL definitions.

I sincerely thank Andrew Dauman from Synplicity and Richard Hall from Cadence Design Systems, Inc for reviewing the book and providing many suggestions.

I especially thank my wife, Gloria Jean, for supporting me in this endeavor.

Preface xix

Sculpture Created by my Wife Gloria to Express my Long Hours with a Laptop in the Creation of VHDL Books

### **About the Author**

**Ben Cohen** is currently a VHDL language trainer and consultant. He has technical experience in digital and analog hardware design, computer architecture, ASIC design, synthesis, and use of hardware description languages for modeling of statistical simulations, instruction set descriptions, and hardware models. He applied VHDL since 1990 to model various bus functional models of computer interfaces. He authored *VHDL Coding Styles and Methodologies*, first and second editions, and *VHDL Answers to Frequently Asked Questions*, first and second editions. He was one of the pilot team members of the VHDL Synthesis Interoperability Working Group of the Design Automation Standards Committee who authored the *IEEE P1076.6 Standard for VHDL Register Transfer Level Synthesis*. He taught several VHDL training classes, and provided VHDL consulting services on several tasks.

**VhdlCohen Training and Consulting**

email: <u>VhdlCohen@aol.com</u>

Web page: http://www.vhdlcohen.com/

or <a href="http://members.aol.com/vhdlcohen/vhdl/">http://members.aol.com/vhdlcohen/vhdl/</a>

Preface xxi

## **DISCLAIMER**

Every attempt was made to ensure accuracy in the specifications and implementation of the models. However, All code provided in this book and in the accompanied CD is distributed with \*ABSOLUTELY NO SUPPORT\* and \*NO WARRANTY\* from the author. The author shall not be liable for damage in connection with, or arising out of, the furnishing, performance or use of the models provided in the book and CD.

The software media is distributed on an "AS IS" basis, without warranty.

If the media is defective, you may return it for a replacement.

Use or reproduction of the information provided in this book and on the enclosed CD for commercial gain is strictly prohibited.

# 1 <u>OVERVIEW</u>

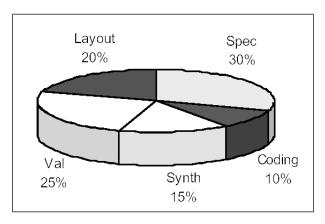

This chapter introduces exemplary design processes required in typical front-end phases of a design. These phases include definition of requirements, architectural design, verification, behavioral modeling, RTL design, synthesis, timing analysis, design applications, documentation and delivery.

#### 1.1 COMPONENT DESIGN PROCESS

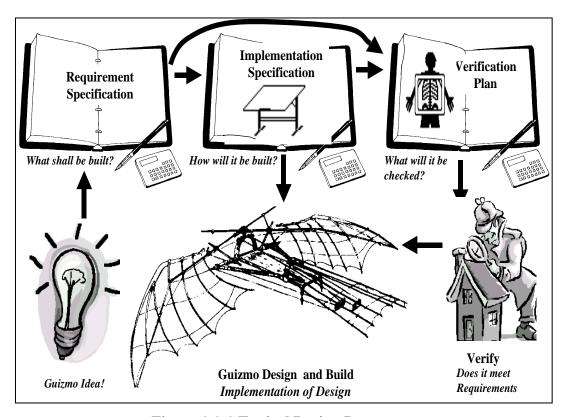

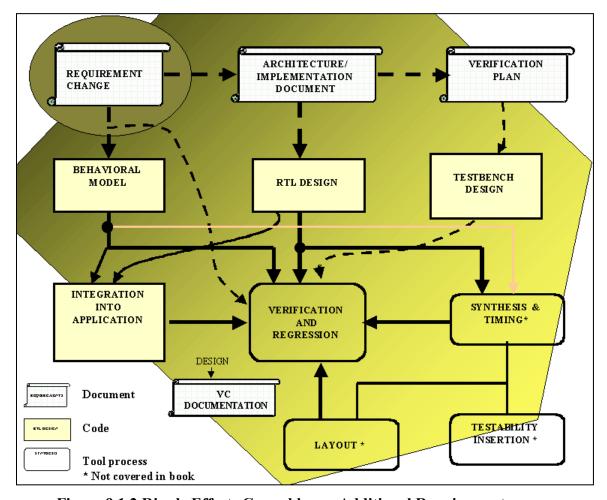

Typical design process and phases Figure 1.1-1 represents typical processes for the definition, implementation, and verification of a design. A design typically starts with an idea (e.g., a house, a car, an ASIC). A **requirement document** identifies what shall be built, and what kind of interfaces, performance,

etc, it must meet (e.g., a house shall be 4000 square feet in size, two-stories, facing the ocean). Based on those design requirements, an **implementation specification** is followed to identify how the design will be built. This is a plan, but not the actual implementation (e.g., the house will have four bedrooms, with sliding windows facing the ocean, and prefabricated purchased appliances). The **verification plan** specifies what and how the product will be checked to insure that it meets the original requirements. The tests require information from both the requirements and the implementation documents. For example, a house may have several inspection steps (e.g., foundation, framing, electrical), and each purchased appliance may have its own separate inspections to insure quality before installation. Once the above documents are approved, the implementation and verification steps can proceed.

Figure 1.1-1 Typical Design Processes

Overview 3

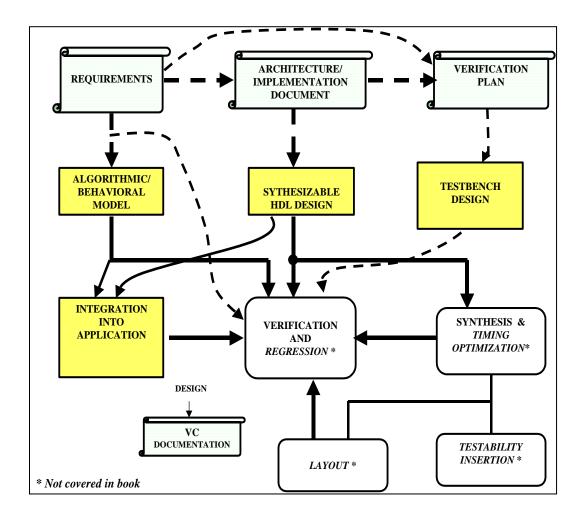

Figure 1.1-2 represents typical component and subblock design processes, with emphasis on the front-end design aspects. Each of these processes is greatly expanded and demonstrated in the subsequent chapters, with complete samples for the documents, HDL code of the models and verification, and compilation scripts for simulation and synthesis.

**Figure 1.1-2 Component Design Processes**

Requirement specification is necessary prior to proceeding with design implementation . It defines operations and required interfaces, but not the implementation

Avoid using the SPIRAL coding methodology.

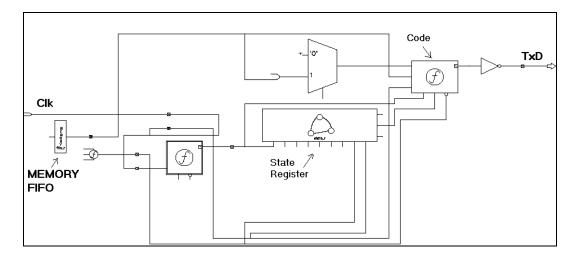

Behavioral Model may validate the requirements

Architectural implementation document defines subblocks, data flow, control flow, and reusable subblocks. Behavioral models may be used as source for the synthesizers

A design typically starts with a **requirement specification** that defines the required operations and interfaces of the component, but not its implementation. This step is necessary to reaffirm the requirements and to remove any ambiguities between the original goals and the implementation. A well-reviewed requirement document brings all personnel involved in the project into an agreement as to what the design (Subblock, FPGA, or ASIC) must do, but **not how it is implemented.** The requirement document can be defined in many formats, and may include English descriptions, behavioral modeling definitions, or language specific definitions such as C, C++, MathCad, VHDL, Verilog, SPEC  $C^{1}$ , etc. Without this document, implementation designs typically must be iterated several times, or completely redone because the objectives of the design (i.e., the requirements) were not specified. That haphazard technique is often called the SPIRAL coding method where the design is hacked, iterated, and generally poorly documented until it meets requirements that are defined on the fly.

Once the requirements are defined, reviewed, and agreed upon, an algorithmic, and not necessarily cycle-accurate **behavioral model** of the design, may be started (if not done during the design requirements phase) and studied for further validation of the requirements.

Following the requirement document, the architectural implementation document can be started. This document identifies the subblocks, data flow, and control flow of the design. These subblocks may also be other components or IPs. This step is necessary to reaffirm how the design will be partitioned, and architectured from a hardware viewpoint to meet the requirements. Again, this step, and the critical peer review of this step is necessary prior to starting a single line of synthesizable behavioral or RTL coding. Otherwise, the coding will typically be iterated several times, or completely redone because the objectives of the design and requirements were not implemented. It is common to mistake the requirement document from the architectural document, or to even accept the architectural implementation document as the requirement document. Those two documents serve different purposes, and it is good practice to create them separately.

<sup>&</sup>lt;sup>1</sup> Spec C: specification Language and Methodology, Daniel D Gajski, Jianwen Zhu, Kluwer Academic Publishers 2000, ISBN 0-7923-7822-9

Overview 5

With the advent of new compiler technology, it is now possible to directly synthesize higher-level definitions from behavioral HDL<sup>2</sup> or C<sup>3</sup> into either lower level RTL code or netlists. The inclusion of these tools into the implementation process needs to be considered during the architectural implementation phase.

Verification plan defines functional verification steps to insure design compliance The **verification plan** defines how the component will be verified to insure that the design meets the requirements. The verification plan makes use of the requirement document for the source of requirements, and the implementation document for the definition of the interfaces of the components, subblocks, or ASIC. It extracts from the requirement document the features to be verified. It also defines the transactions and types of vectors (directed or random) to be applied to the design, the

methods of test vector applications, and the techniques used to verify compliance to the functional specifications.

The synthesizable **behavioral** and **RTL designs** make use of the architectural requirement document as the source of design requirements. As each piece of the subblock is defined, it is recommended that the code be checked with both linting<sup>4</sup> and synthesis tools. The linting tool identifies errors in coding rules and style, and provides design warnings. A good synthesizer provides linting information, including synthesis-coding violations. In addition, the synthesizer provides information about the design including 1) identification of the registers, 2) unused inputs and outputs, 3) write-only hardware that gets optimized out, 4) and graphical views of the design and interconnects for use as a sanity check of the hardware inferred by the HDL. The goals of using the synthesis toolset at this phase of the design process is only to help in the debug and understanding of the design, but not necessarily to optimize the design for performance, unless blatant inadequacies are observed.

To maintain interoperability among commercial tools, it is important that the RTL design abides by coding rules and design style guides such as the *IEEE 1076.6 VHDL RTL for synthesis guidelines*<sup>5</sup>, *IEEE P1364.1 Standard for Verilog*® Register Transfer Level Synthesis, and Nonblocking Assignments in Verilog

\_

<sup>&</sup>lt;sup>2</sup> Example: YXI Y Explorations, Inc., http://www.yxi.com/

<sup>&</sup>lt;sup>3</sup> C Level Design, http://www.cleveldesign.com/

<sup>&</sup>lt;sup>4</sup> Examples: http://www.novas.com, http://www.Transeda.com

<sup>&</sup>lt;sup>5</sup> http://www.vhdl.org/siwg

Synthesis, Coding Styles that Kill<sup>6</sup>. Deviations from those standards need to be documented with rationales. Other proprietary guidelines, such as coding and documentation styles, are necessary to achieve design consistency and potential reuse.

use of requirements. verification plan. and implementation document

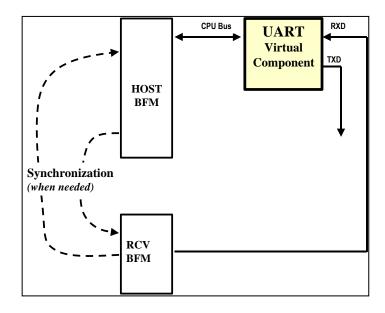

Testbench makes The **testbench design** typically occurs (or should occur) concurrently with the RTL design by a verification engineer. The testbench is written for the verification of the subblocks, the integration of subblocks, and the component design. The testbench is based on the verification plan, requirement and implementation documents. The purpose of the testbench is to provide an environment to verify that the implemented design meets the requirements.

Verification ensures design accuracy

The **verification** phase makes use of the testbench and the designs under test, including the source models (e.g., behavioral, RTL, C), the synthesized models, and any application software. Verification is a very demanding and important process to insure that the design functions correctly in the intended system.

Back-end processes must meet requirements

Synthesis, testability, layout, and timing analysis are important back-end processes necessary for the fabrication of the design to the desired requirements.

6http://www.deepchip.com/items/0347-01.html

http://www.sunburst-

design.com/papers/CummingsSNUG2000SJ NBA rev1a.pdf (included on CD in Verilog subdirectory for user's convenience)

# 2 <u>REQUIREMENT</u> <u>SPECIFICATION</u>

This section describes the requirement specification for an RS232 UART design. The purpose of this chapter is to demonstrate, by example, a model of a requirement specification. A serious attempt was made to include topics pertinent to all components. However, every design has its own peculiarities, and additional entries need to be identified for specific designs. The reviewers may disagree with the features presented in this specification. If the reviewers have comments, then that specification has met its goals of providing a forum for a good design review. Again, the purpose of this book is to demonstrate methodologies and provide techniques using the UART model as an model, rather than just designing a UART. There are several methods to define requirement specifications including English language and programming languages such as VHDL, C, C++, SPEC C, *MathCad*, *Foresight*<sup>1</sup>, etc. Programming languages have the advantages of creating an executable specification. However, there are several requirements that are difficult to express in a programming language. For example, operating conditions (e.g., clock speed, operating range, radiation levels, size, reliability, reset values, latency, packaging) are design attributes rather than processing algorithms, which cannot be expressed in a programming language that does not support attributes. In general, it is best to use an English specification document as a baseline to cover all the requirements of the design. This English document can reference other executable specification models for the definition of specific

<sup>1</sup> http://www.foresight.com

algorithms that are best expressed mathematically. This creates a universal document that does not require knowledge of programming languages as the baseline for the requirements, but allows the inclusion of other requirement models for further definitions. The English specification used in this book is modeled after a modified structure proposed in *Military Standard MIL-STD-490A*<sup>2</sup>, 4 June 1985, Specification Practices document. This is a Department of Defense (DoD) document approved for public release with unlimited distribution. This Military Standard sets forth practices for the preparation, interpretation, change, and revision of program-peculiar specifications prepared by or for the Departments and Agencies of the Department of Defense. It defines good practices for defining requirements.

Another source of specification modeling template used in this sample requirement document is MIL-STD-1553 standard (*Aircraft Internal Time Division Command/Response Multiplex Data Bus*), another DoD document approved for public release with unlimited distribution.

#### 2.1 LANGUAGE

Engineers are notorious for being poor writers. This section emphasizes important English points to consider when writing a document because they typically are major sources of errors and poor style.

**STYLE:** MIL-STD-490 section 3.2.3, language style, states the following: The paramount consideration in a specification is its technical essence, and this should be presented **in language free of vague and ambiguous terms** and using the simplest words and phrases that will convey the intended meaning. Inclusion of essential information shall be complete, whether by direct statements or references to other documents. Consistency in terminology and organization of material will contribute to the specification's clarity and usefulness. Sentences shall be as short and concise as possible. Punctuation should aid in reading and prevent misreading. Well-planned word order requires a minimum of punctuation. When extensive punctuation is necessary for clarity, the sentence(s) shall be rewritten. Sentences with compound clauses shall be converted into short and concise

\_

sentences.

<sup>&</sup>lt;sup>2</sup> Mil-STD-490A is included on CD

**Commonly used words and phrasing**. Certain words and phrases are frequently used in a specification. The following rules shall be followed:

- a. Referenced documents shall be cited thus <u>"conforming to ..."</u> "<u>as specified in ..."</u> or "in accordance with ...".

- b. "<u>Unless otherwise specified</u>" shall be used to indicate an alternative course of action. The phrase shall always come at the beginning of the sentence, and if possible, at the beginning of the paragraph. This phrase shall be used only when it is possible to clarify its meaning by providing a reference such as to Section 6 of the specification for further clarification in the contract or order or otherwise.

- c. When making reference to a requirement in the specification and the requirement referenced is rather obvious or not difficult to locate, the simple phrase "as specified herein" is sufficient and should be used.

- d. The phrase "... to determine compliance with ..." or "... to determine conformance to ..." should be used in place of "... to determine compliance to ...". In any case use the same wording throughout.

- e. In stating positive limitations, the phrase shall be stated thus: "The diameter shall be no greater than ...".

The emphatic form of verb <u>shall</u> be used throughout the specification; i.e., state in the requirements section that "The indicator shall be designated to indicate ...", and in the section containing test provisions "The indicator shall be turned to zero and 230 volts alternating current applied." For specific test procedures, the imperative form may be used provided the entire method is preceded by "the following tests shall be performed," or related wording. Thus, "Turn the indicator to zero and apply 230 volts alternating current."

Use of "shall," will," "should," and "may". Use "shall" whenever a specification expresses a provision that is binding. Use "should" and "may" wherever it is necessary to express non-mandatory provisions. "Will" may be used to express a declaration of purpose on the part of the contracting agency. It may be necessary to use "will" in cases where the simple future tense is required, i.e., power for the motor will be supplied by the ship.

THAT verses WHICH: Another common mistake is the misunderstanding in the

use the pronoun *THAT* and *WHICH*. The Merriam-Webster<sup>3</sup> dictionary defines: that pron, pl those: 1: the one indicated, mentioned, or understood <that is my house> 2: the one farther away or first mentioned <this is an elm, that's a maple> 3: what has been indicated or mentioned <after that, we left> 4: the one or ones: IT, THEY <those who wish to leave may do so>

which pron 1: which one or ones <which is yours> ... 3 — used to introduce a relative clause and to serve as a substitute therein for the noun modified by the clause <the money, which is coming to me,>

Microsoft Word grammar check explains the application rule as: "if the marked group of words is essential to the meaning of the sentence, use that to introduce the group of words. Do not use a comma. If these words are not essential to the meaning of your sentence, use which and separate the words with a comma". For example,

Books, which are generally expensive, can be purchased over the Internet. *Note: The qualifier "which are generally expensive" is not essential to the meaning of the sentence.*

The book that describes VHDL guidelines is the Cohen book.

Note: The qualifier "that describes VHDL guidelines" is essential in the sentence.

In some sentence structures, the qualifier *THAT* can be deleted, thus shortening the sentence, without affecting the meaning of the sentence. For example,

Spec C is a language  $\underline{\text{that is}}$  suitable for specifying systems. // can delete "that is"

Spec C is a language suitable for specifying systems.

\_

$<sup>^3</sup>$  © 1995 Zane Publishing, Inc. The Merriam-Webster Dictionary © 1994 by Merriam-Webster, Incorporated

#### 2.2 UART REQUIREMENT SPECIFICATION

Header page Pertinent logistics data about the requirements REQUIREMENTS FOR AN ASYNCHRONOUS OR SYNCHRONOUS 8 TO 32 BIT Universal Asynchronous Receiver/Transmitter

| Document #:        |  |

|--------------------|--|

| Release Date:      |  |

| Revision Number:   |  |

| Revision Date:     |  |

| Originator         |  |

| Name:              |  |

| Phone:             |  |

| email:             |  |

| _                  |  |

| Approved:          |  |

| Name:              |  |

| Phone:             |  |

| email:             |  |

|                    |  |

|                    |  |

| Revisions History: |  |

| Date:              |  |

| Version:           |  |

| Author:            |  |

| Description:       |  |

| 2 2 2 3 P          |  |

| •••                |  |

Note: The Header page will vary with each organization because of different needs. For example, a reviewer list (with name and signature only) may be more appropriate that a single "approved" entry. This page is a placeholder for a header page, and is not meant to represent an absolute format.

The numbering system for the requirement specification starts at 1.0 because it is intended to represent a stand-alone document. Therefore, it does not follow the chapter numbering system.

#### 1. SCOPE

1.1 Scope

Concise abstract of the coverage of the specification

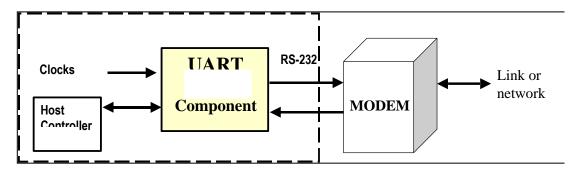

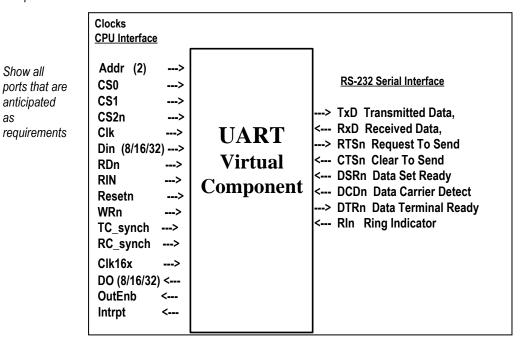

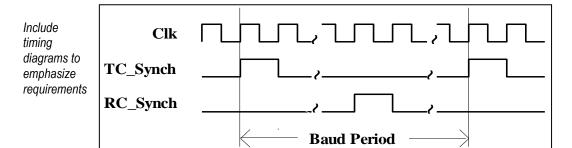

This document establishes the requirements for a component that provides a bridge between a microprocessor interface and a transmit/receive asynchronous or synchronous, parameterized eight to thirty-two bit serial interface, emulating a UART-like protocol.

Target audience

The specification is primarily targeted for component developers, IP

integrators, and system OEMs.

Purpose of specification

1.2 Purpose

These requirements shall apply to a modified Universal

Asynchronous Receiver/Transmitter (UART) interface for inclusion

System, hardware.

as a component.

software 1.3 Classification

This document defines the requirements for a hardware design.

#### 2. DEFINITIONS

Terms used

in this document. Organize definitions

alphabeticall

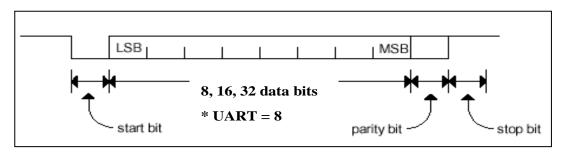

2.1 Asynchronous transmission<sup>4</sup>

The transmitted clock is not sent to the receiving logic. Instead,

asynchronous transmission relies on some other mechanism to synchronize the receiver to the data stream. In the case of a UART, asynchronous transmission relies on the use of a start bit and stop bit(s), in addition to the bits representing the character (and an

optional parity bit), to distinguish separate characters.

### 2.2 Baud rate<sup>4</sup>

The baud rate is the number of events, or signal changes, that occur in one second.

#### **2.3 DTE**

Data Terminal Equipment, such as terminals.

#### **2.4 DCE**

Data Communication Equipment, such as modems.

#### 2.5 Framing Error

A condition where the received data stream is not properly framed between a START bit and a STOP bit.

#### 2.6 Overrun Error<sup>4</sup>

An error that occurs when a device receiving data cannot handle or make use of

the information as rapidly as it arrives.

#### 2.7 Parity<sup>4</sup>

The quality of sameness or equivalence, in the case of computers usually referring to an error-checking procedure in which the number of ONEs must always be the same—either even or odd—for each group of bits transmitted without error.

Even parity The number of ONEs in each successfully transmitted set of bits (data plus parity) must be an even number.

The number of ONEs in each successfully transmitted set of bits (data plus parity) must be an odd number.

No parity bit is used. No parity

Space parity A parity bit is used and is always set to zero.

Mark parity A parity bit is used and is always set to one.

#### 2.8 Start Bit

A low level bit to indicate the start of a transmission. The receiver uses this negative transition to synchronize its internal clock to the transmitted data.

#### 2.9 Stop Bit

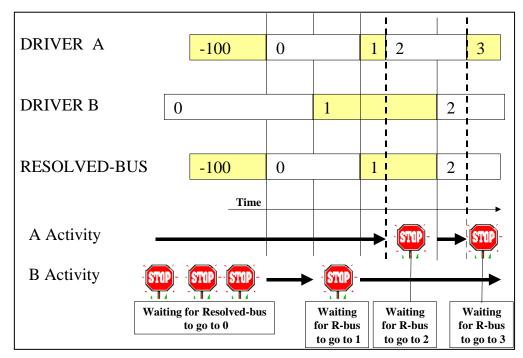

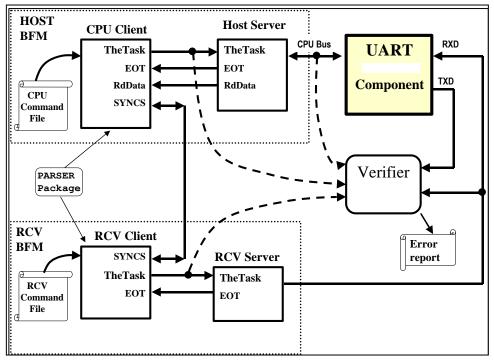

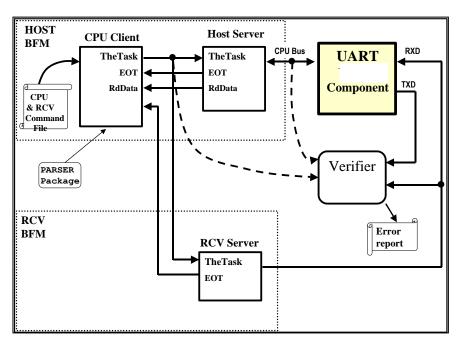

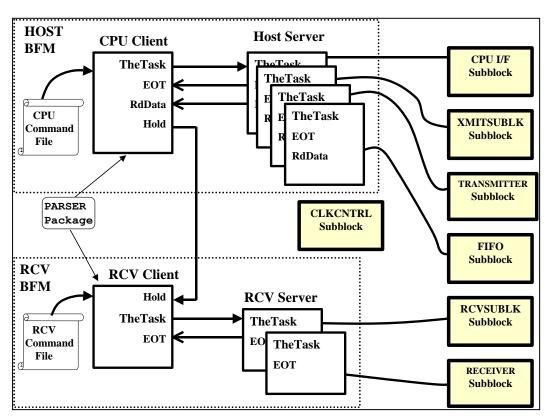

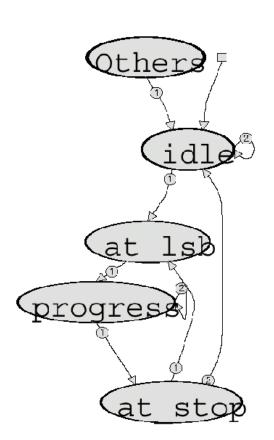

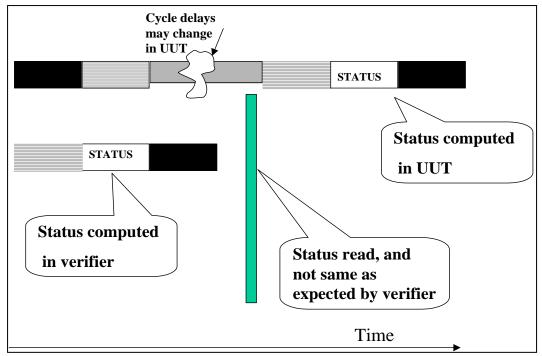

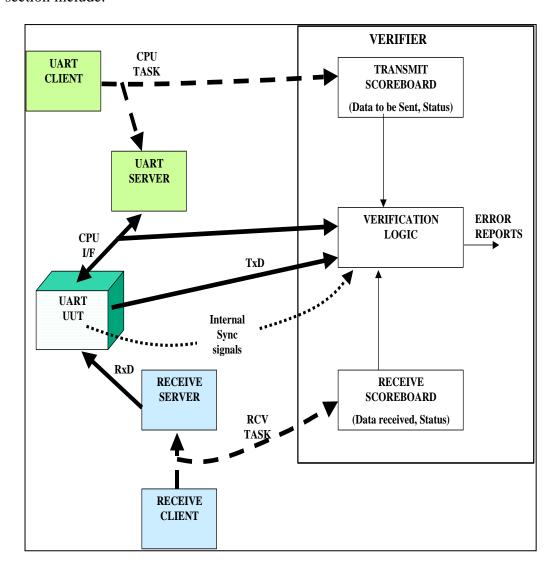

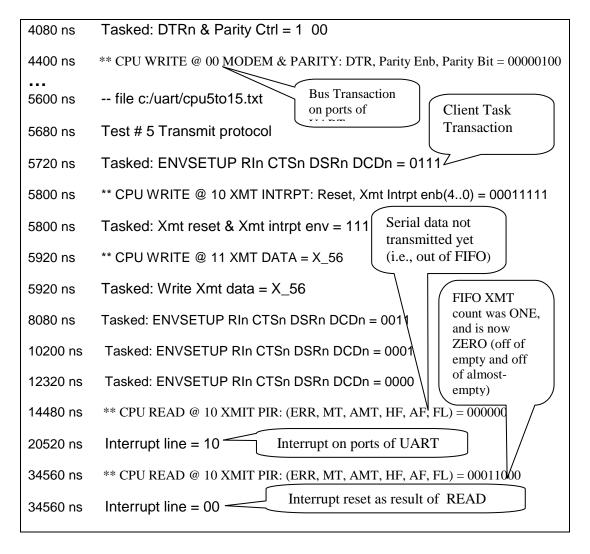

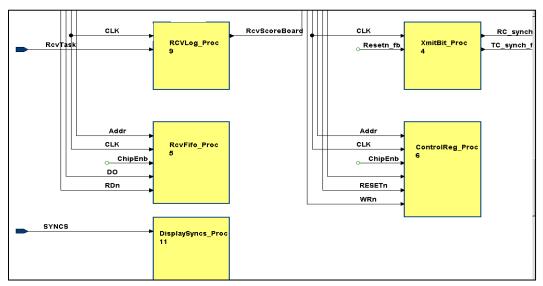

A high level bit to indicate the end of a transmission, and to guarantee that a new START bit will be initiated with a negative edge. STOP bits are also asserted when no data is sent.