| REQUIREMENTS FOR A SYNCHRONOUS FIFO,<br>First-In First-Out Buffer                                                                                                                          |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Document #:<br>Release Date:<br>Revision Number<br>Revision Date:<br>Originator<br>Name:<br>Phone:<br>email:                                                                               | fifo_req_001<br>:<br><br> |

| Approved:<br>Name:<br>Phone:<br>email:                                                                                                                                                     |                           |

| Revisions History :<br>Date:<br>Version:<br>Author:<br>Description:<br>Synchronous FIFO to be used as an IP. FIFO management (e.g., push, pop, error<br>handling) is external to the FIFO. |                           |

|                                                                                                                                                                                            |                           |

|                                                                                                                                                                                            |                           |

|                                                                                                                                                                                            |                           |

# 1. SCOPE

### 1.1 Scope

This document establishes the requirements for an Intellectual Property (IP) that provides a synchronous First-In First-Out (FIFO) function.

The specification is primarily targeted for component developers, IP integrators, and system OEMs.

## 1.2 Purpose

These requirements shall apply to a synchronous FIFO with a simple interface for inclusion as a component. This requirement includes SystemVerilog assertions to further clarify the properties of the FIFO.

### **1.3 Classification**

This document defines the requirements for a hardware design.

# 2. DEFINITIONS

### 2.1 PUSH

The action of inserting data into the FIFO buffer.

## 2.2 POP

The action of extracting data from the FIFO buffer

## **2.3 FULL**

The FIFO buffer being at it maximum level.

## **2.4 EMPTY**

The FIFO buffer with no valid data.

### 2.5 Read and Write Pointers

Pointers represent internal structure of the FIFO to identify where in the buffer data will be stored (write pointer,  $wr_ptr$ ), or be read (read pointer,  $rd_ptr$ )

# **3. APPLICABLE DOCUMENTS**

**3.1 Government Documents** None**3.2 Non-government Documents** None

# 4. ARCHITECTURAL OVERVIEW

### 4.1 Introduction

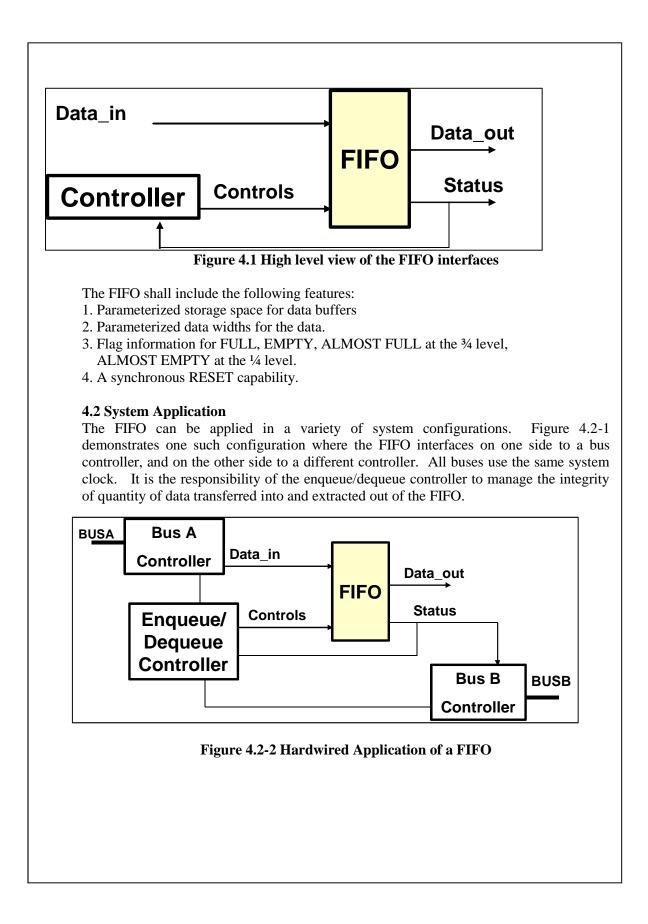

The FIFO component shall represent a design written in SystemVerilog with SystemVerilog assertions. The FIFO shall be <u>synchronous</u> with a single clock that governs both reads and writes. The FIFO typically interfaces to a controller for the synchronous pushing and popping of data. Figure 4.1 represents a high level view of the interfaces.

<sup>&</sup>lt;sup>58</sup> The complete SystemVerilog interface with assertions is in file *ch6/fifo\_if.sv*

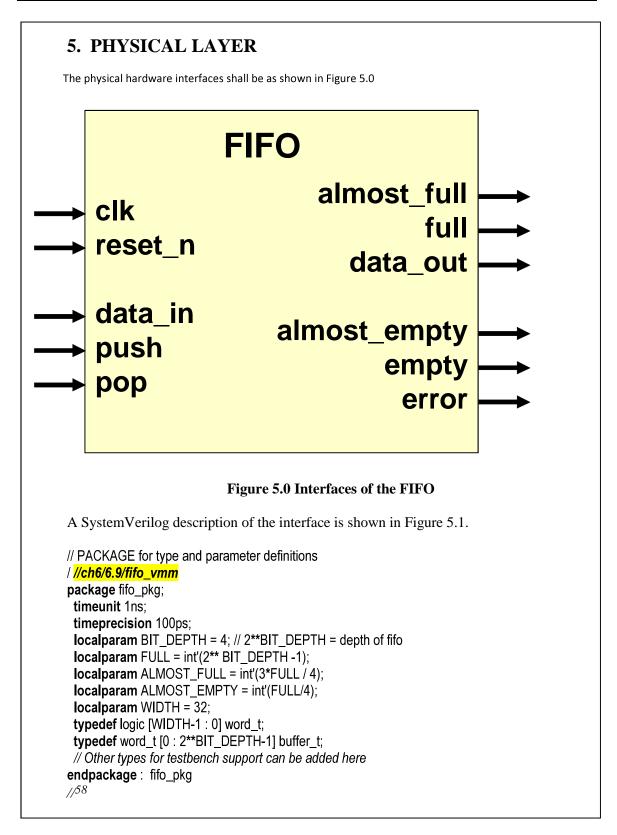

// INTERFACE of FIFO interface fifo\_if(input clk, reset\_n); import fifo\_pkg:: \*; // access to package logic push; // push data into the fifo **logic** pop; // pop data from the fifo logic almost\_full; // fifo is at 3/4 maximum level logic almost empty; // fifo is at 1/4 maximum level logic full; // fifo is at maximum level logic empty; // fifo is at the zero level (no data) **logic** error; // fifo push or pop error word t data in; word t data out; // FIFO DUV, FIFO Slave interface Interface description with modport fslave\_if ( modports clarifies the use of output empty, the ports. Maintain ordering output almost empty, convention: outputs first, inputs last. output almost full, output full, output data out, input data in, input push, input pop); // FIFO driver, FIFO Driver interface Used by application modport fdrvr\_if ( interfaced to the FIFO output data in. output push, output pop, input empty. input almost empty, input almost full, input full, input data out); *// tasks / sequences / properties / assertions shall be added here.* endinterface : fifo if Figure 5.1 SystemVerilog FIFO interface **5.1 Interface port description**

The individual port elements in the interface in figure 5.1 are described in this section with requirements on them captured as assertions. Since some of the ports describe data intensive portion of the system (such as the data being popped from the FIFO), some of the SystemVerilog testbench features such as queues and tasks are used to capture their requirements. Since these tasks and queues are meant solely for the purpose of specification and verification, and do not have a direct correlation to the hardware implementation of the FIFO, they are declared in the interface itself:

```

// Data queue for verification.

Data Queue

// Queue, maximum size is 2**BIT DEPTH

word_t dataQ [$:2**BIT_DEPTH-1];

// Data read from queue

word_t data_fromQ;

// Push and Pop tasks

task pop_task;

begin

data_in <= 'X; // unsized Xs

pop <= 1'b1;

data_fromQ <= dataQ.pop_front();</pre>

@ (posedge clk);

end

endtask : pop_task

task push_task (word_t data);

begin

$display ("%0t %m Push data %0h ", $time, data);

data in <= data; //data to be written

Input data stored into FIFO

push \leq 1'b1;

buffer 1 cycle following the

dataQ.push_back(data); // push to dataQ

push control.

@ (posedge clk);

end

endtask : push_task

task idle_task(int num_idle_cyles);

begin

push \leq 1'b0;

Use immediate assertion for

pop \le 1'b0;

simple, local checks.

data in <= 'X;

assert (num idle cycles < 10000) else

$warning ("%0t %0m idle task is invoked with LARGE number of idle cycles %0d ",

num_idle_cycles);

repeat (num_idle_cycles) @ (posedge clk);

end

endtask : idle_task

```

## 5.1.1 Data input/output

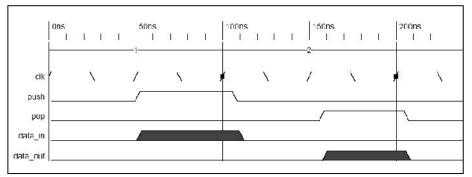

Figure 5.1.1 provides a timing diagram of the interface.

## Figure 5.1.1 FIFO Interface Timing Diagram

### 5.1.1.1 Data\_in

Direction: Input, Peripheral -> FIFO;

Size: Determined by WIDTH parameter; Active level: High

Data sent from a peripheral device to the FIFO under the control of the *push* control.

#### 5.1.1.2 Data\_out

Direction: Output, FIFO -> Peripheral;

Size: Determined by WIDTH parameter; Active level: High

FIFO data sent to a peripheral device under the control of *pop* signal.

#### 5.1.2 Push / Pop 5.1.2.1 push

Direction: Input, Peripheral -> FIFO; Size: 1 bit, Active level: high

When *push* is active, *data\_in* shall be stored into the FIFO buffer at the next clock cycle. It is an error if a push with no pop control occurs on a full FIFO. The following property characterizes these requirements:

// never a push and full and no pop sequence q\_push\_error; !(push && full && !pop); endsequence : q\_push\_error cq\_push\_error : cover sequence (@(posedge clk) q\_push\_error); ap\_push\_no\_pop: assert property(@ (posedge clk) push |-> !full || pop);

## 5.1.2.2 рор

Direction: Input, Peripheral -> FIFO; Size: 1 bit, Active level: high

When *pop* is active, *data\_out* shall carry the data that was first stored into the FIFO, but was not yet popped. The *data\_out* shall be asserted in the same cycle of *pop* control. It is an error if a pop control occurs on an empty FIFO. The following properties and task characterize these requirements:

```

// Data out timing and data integrity

property p_pop_data;

pop |-> data_out == data_fromQ;

// from 5.1 pop_task

endproperty : p_pop_data

ap_pop_data : assert property (@ (posedge clk) p_pop_data);

```

// never a pop on empty

sequence q\_pop\_error;

! (pop && empty && !push);

endsequence : q\_pop\_error

cq\_pop\_error : cover sequence (@

Could also use the **let** construct: **let** q\_pop\_error = ! (pop && empty && !push);

cq\_pop\_error : cover sequence (@ (posedge clk) q\_pop\_error); ap\_pop\_nopush: assert property(@ (posedge clk) pop |-> !empty || push);

## 5.1.2.3 Push-Pop Data Sequencing

Data entered into the FIFO buffer shall be outputted in the same order that it is entered. The *push\_task* and *pop\_task* tasks, and the properties characterized in sections 5.1.2.1 and 5.1.2.2 define the ordering sequence. Specifically, data pushed in the back of the FIFO buffer is extracted from the front of the buffer in a first-in, first-out manner.

### 5.1.3 Status flags 5.1.3.1 Full

Direction: Output, FIFO -> Peripheral ; Size: 1 bit, Active level: high

When the FIFO reaches the maximum depth of the buffer, as defined by the parameter BIT\_DEPTH, then the *full* flag shall be active. The following sequence and property characterize this requirement:

sequence gFull;

dataQ\_size == BIT\_DEPTH; endsequence : qFull Could also use the **let** construct: **let** qFull = dataQ\_size == BIT\_DEPTH;

property p\_fifo\_full; qFull |-> full; endproperty : p\_fifo\_full ap\_fifo\_full : assert property (@ (posedge clk) p\_fifo\_full);

## 5.1.3.2 Almost full

Direction: Output, FIFO -> Peripheral ; Size: 1 bit, Active level: high

When the number of entries in the FIFO reaches or is greater than the predefined value of <sup>3</sup>/<sub>4</sub> of the maximum depth of the buffer, as defined by the parameter ALMOST\_FULL, then the *almost\_full* flag shall be active. The following sequence and property characterizes this requirement:

**sequence** qAlmost\_full;

dataQ\_size >= ALMOST\_FULL;

endsequence : qAlmost\_full

Could also use the **let** construct: **let** qAlmost\_full = dataQ\_size >= ALMOST\_FULL; property p\_fifo\_almost\_full; qAlmost\_full |-> almost\_full; endproperty : p\_fifo\_almost\_full ap\_fifo\_almost\_full : assert property (@ (posedge clk) p\_fifo\_almost\_full);

## 5.1.3.3 Empty

Direction: Output, FIFO -> Peripheral ; Size: 1 bit, Active level: high

When all the enqueued data has been dequeued, then the *empty* flag shall be active. A reset shall cause the empty flag to be active. The following sequence and properties characterize these requirements:

// sequence definition, use in cover for empty

**sequence** qEmpty;

dataQ\_size==0; endsequence : gEmpty Could also use the **let** construct: **let** qEmpty = dataQ\_size==0;

property p\_fifo\_empty; qEmpty |-> empty;

endproperty : p\_fifo\_empty

ap\_fifo\_empty : **assert property (**@ (**posedge** clk) p\_fifo\_empty); The property for the flags at reset time is defined in section 5.1.4.

### 5.1.3.4 Almost empty

Direction: Output, FIFO -> Peripheral ; Size: 1 bit, Active level: high

When the number of entries in the FIFO reaches or is less the predefined value of <sup>1</sup>/<sub>4</sub> of the maximum depth of the buffer, as defined by the parameter ALMOST\_EMPTY, then the *almost\_empty* flag shall be active. The following sequence and property characterize this requirement:

sequence qAlmost\_empty; dataQ\_size <= ALMOST\_EMPTY; endsequence : qAlmost empty Could also use the **let** construct: **let** qAlmost\_empty = dataQ\_size <= ALMOST\_EMPTY;

property p\_fifo\_almost\_empty; qAlmost\_empty |-> almost\_empty; endproperty : p\_fifo\_almost\_empty ap\_fifo\_almost\_empty : assert property (@ (posedge clk) p\_fifo\_almost\_empty);

## 5.1.4 Reset

Direction: Input, Peripheral -> FIFO ; Size: 1 bit, Active level: low

The *reset\_n* is an active low reset control that clears the pointers and the status flags. The *reset\_n* is asynchronous to the system clock *clk*. See properties defined in section 5.1.3.3 for the behavior of the empty flag when *reset\_n* is asserted in the FIFO.

# property p\_fifo\_ptrs\_flags\_at\_reset;

!reset\_n |-> ##[0:1] !almost\_empty && ! full && !almost\_full && empty;

endproperty : p\_fifo\_ptrs\_flags\_at\_reset

ap\_fifo\_ptrs\_flags\_at\_reset : assert property (@ (posedge clk)

p\_fifo\_ptrs\_flags\_at\_reset);

#### 5.15 Clock

<u>Direction: Input, Peripheral -> FIFO ; Size: 1 bit, Active edge: rising edge</u> The *clk* clock is the synchronous system clock for both the read and write transactions; it is active on the positive edge of the clock. The clock shall be at 50% duty cycle.

#### 5.16. Error

<u>Direction: Output, FIFO -> Peripheral; Size: 1 bit, Active level: high</u> When either an overflow (push on full) or underflow (pop on empty) error has occurred, the error flag shall be asserted. The following properties characterize the *error* output.

// Reusing the q\_push\_error and q\_pop\_error definitions,

property p\_error\_flag;

q\_push\_error or q\_pop\_error |=> error;

endproperty : p\_error\_flag

ap\_error\_flag : assert property ( @ (posedge clk) p\_error\_flag);

## **6. PROTOCOL LAYER**

The FIFO operates on single word writes (push) or single word reads (pop).

## 7. ROBUSTNESS

#### 7.1 Error Detection

The FIFO shall lump all overflow (push on full) or underflow (pop on empty) errors as a single error output. See 5.16 for details.

# 8. HARDWARE AND SOFTWARE

### 8.1 Fixed Parameterization

The FIFO shall provide the following parameters used for the definition of the implemented hardware during hardware build:

BIT\_DEPTH where 2\*\*BIT\_DEPTH represents the depth of FIFO.

WIDTH represents the data width.

ALMOST\_FULL (0.75 \* (2 \*\* BIT\_DEPTH))

ALMOST\_EMPTY (0.25 \* (2 \*\* BIT\_DEPTH))

### 8.2 Software interfaces

The FIFO shall enter input data (*data\_in*) into the FIFO buffer when the *push* control is active. It shall provide data from the buffer upon an activation of the *pop* control. See 5.1.2 Push / Pop for definition of the properties that characterize these controls. The FIFO contains no internal registers that can be configured.

This section typically contains the internal registers that the software can access and configure.

# 9. PERFORMANCE

#### 9.1 Frequency

The FIFO shall support a maximum rate of 25 MHz.

### 9.2 Power dissipation

The power shall be less than 0.01 watt at 25 MHz.

## 9.3 Environmental

Does not apply.

### 9.4 Technology

The design shall be adaptable to any technology because the design shall be portable and defined in SystemVerilog RTL.

## **10. TESTABILITY**

None required.

## 11. Mechanical

Does not apply.

## 12. Backup information

A copy of the FIFO interface model and supporting package is included in the download files.

## 6.9.2 Test Plan

The following demonstrates the application of assertions in a verification plan to clarify the verification goals and milestones.

# FIFO Requirements Example